Reset and clock control (RCC) UM0306

60/519

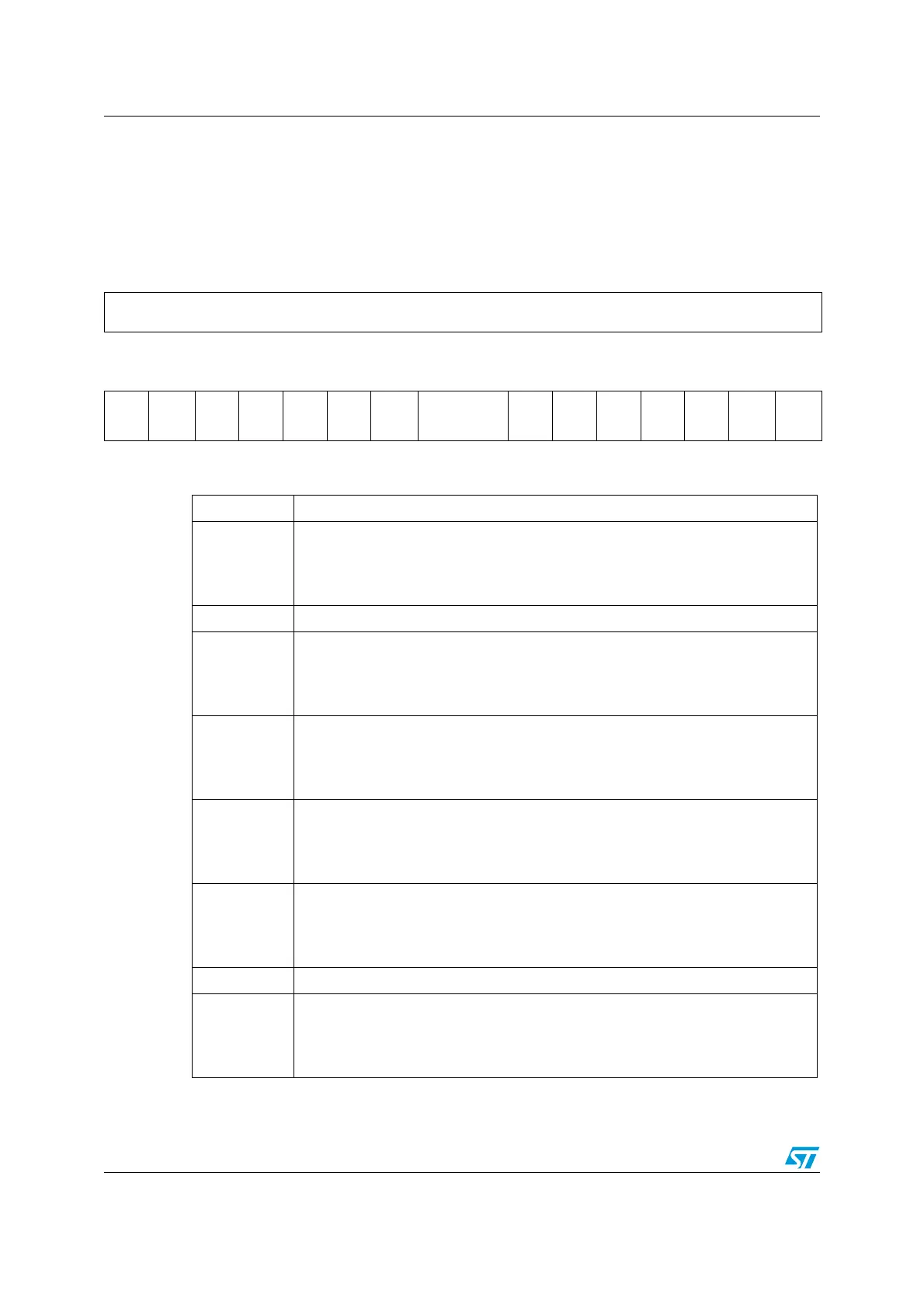

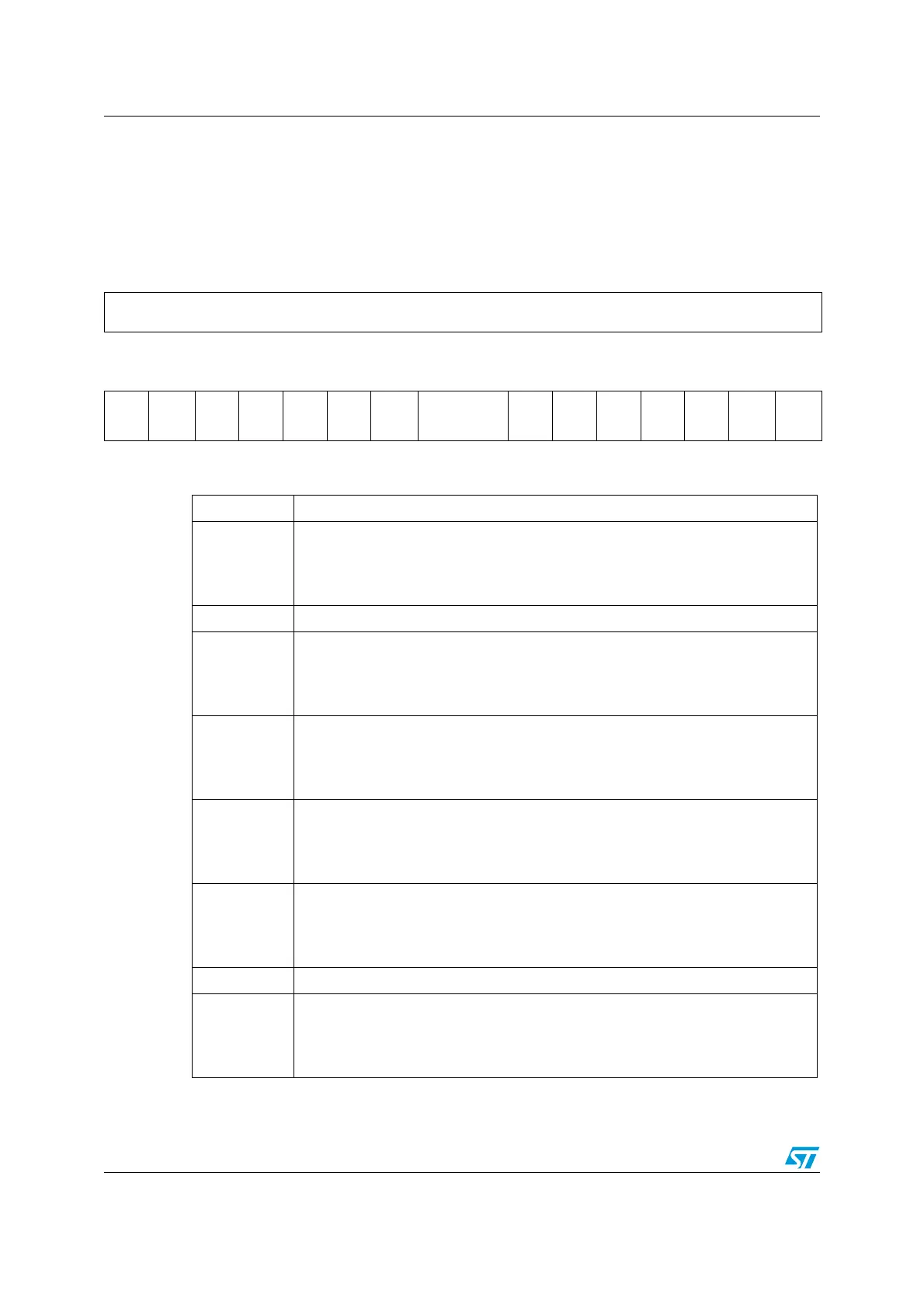

4.3.4 APB2 Peripheral reset register (RCC_APB2RSTR)

Address offset: 0Ch

Reset value: 0000 0000h

Access: no wait state, word, half-word and byte access

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109 87654321 0

Res.

USART

1

RST

Res.

SPI1

RST

TIM1

RST

ADC2

RST

ADC1

RST

Reserved

IOPE

RST

IOPD

RST

IOPC

RST

IOPB

RST

IOPA

RST

Res.

AFIO

RST

rw rw rw rw rw rw rw rw rw rw rw

Bits 31:15 Reserved, always read as 0.

Bit 14

USART1RST USART1 reset

Set and reset by software.

0: No effect

1: Reset USART1

Bit 13 Reserved, always read as 0.

Bit 12

SPI1RST SPI 1 reset

Set and reset by software.

0: No effect

1: Reset SPI 1

Bit 11

TIM1RST TIM1 Timer reset

Set and reset by software.

0: No effect

1: Reset TIM1 timer

Bit 10

ADC2RST ADC 2 interface reset

Set and reset by software.

0: No effect

1: Reset ADC 2 interface

Bit 9

ADC1RST ADC 1 interface reset

Set and reset by software.

0: No effect

1: Reset ADC 1 interface

Bits 8:7 Reserved, always read as 0.

Bit 6

IOPERST IO port E reset

Set and reset by software.

0: No effect

1: Reset IO port E

Loading...

Loading...