Universal synchronous asynchronous receiver transmitter (USART) UM0306

384/519

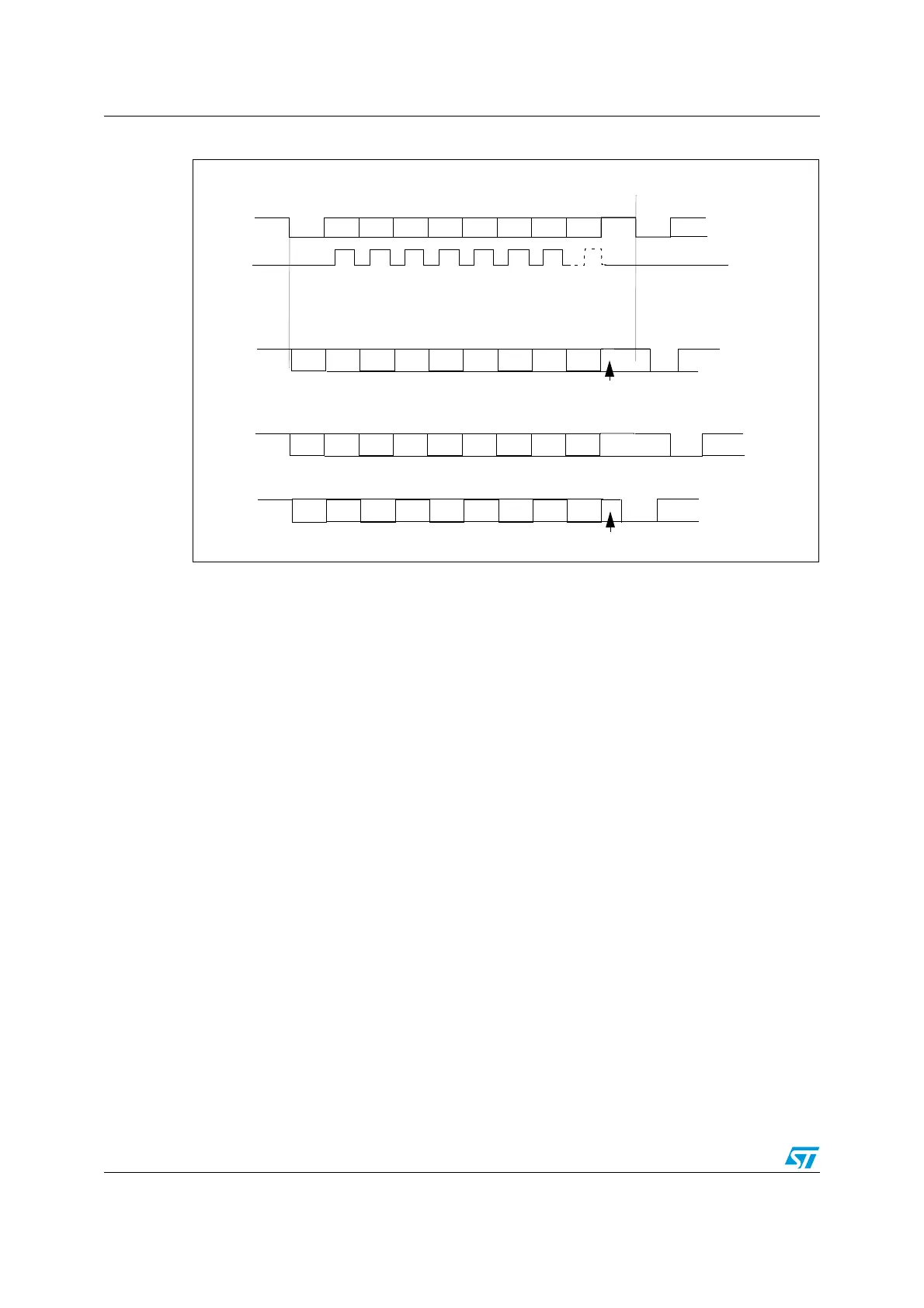

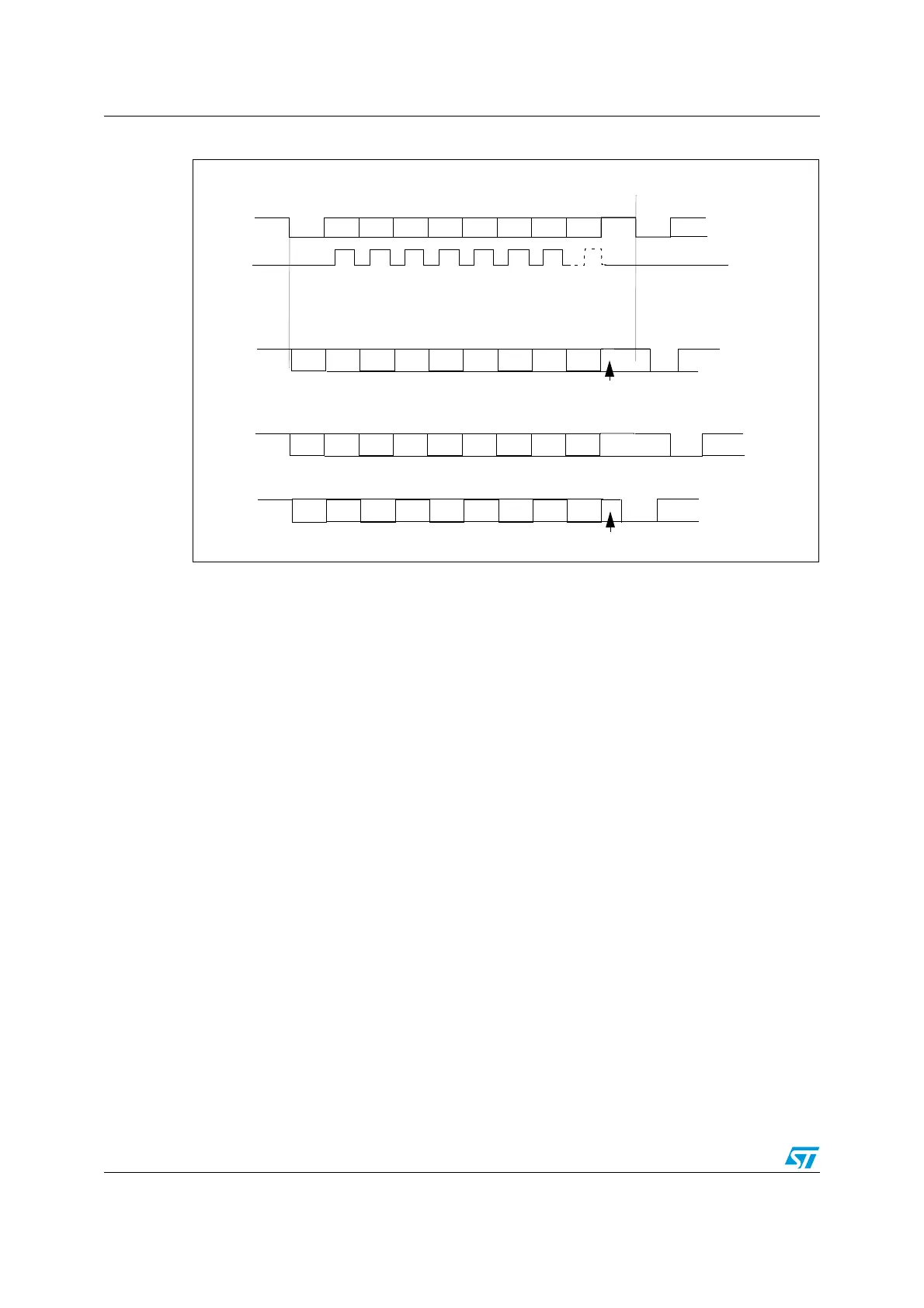

Figure 146. Configurable stop bits

Procedure:

1. Enable the USART by writing the UE bit in USART_CR1 register to 1.

2. Program the M bit in USART_CR1 to define the word length.

3. Program the number of stop bits in USART_CR2.

4. Select DMA enable (DMAT) in USART_CR3 if Multi buffer Communication is to take

place. Configure the DMA register as explained in multi-buffer communication.

5. Set the TE bit in USART_CR1 to send an idle frame as first transmission.

6. Select the desired baud rate using the USART_BRR register.

7. Write the data to send in the USART_DR register (this clears the TXE bit). Repeat this

for each data to be transmitted in case of single buffer.

Single byte communication

Clearing the TXE bit is always performed by a write to the data register.

The TXE bit is set by hardware and it indicates:

● The data has been moved from TDR to the shift register and the data transmission has

started.

● The TDR register is empty.

● The next data can be written in the USART_DR register without overwriting the

previous data.

This flag generates an interrupt if the TXEIE bit is set.

When a transmission is taking place, a write instruction to the USART_DR register stores

the data in the TDR register and which is copied in the shift register at the end of the current

transmission.

Bit0

Bit1

Bit2

Bit3

Bit4

Bit5

Bit6

Bit7

Start

Bit

Stop

Bit

Next

Start

Bit

8-bit Word length (M bit is reset)

Possible

Parity

Bit

Data Frame

Next Data Frame

****

** LBCL bit controls last data clock pulse

CLOCK

**

Bit0

Bit1

Bit2

Bit3

Bit4

Bit5

Bit6

Bit7

Start

Bit

2 Stop

Bits

Next

Start

Bit

Possible

Parity

Bit

Data Frame

Next Data Frame

Bit0

Bit1

Bit2

Bit3

Bit4

Bit5 Bit6

Bit7

Start

Bit

Next

Start

Bit

Possible

Parity

Bit

Data Frame

Next Data Frame

1/2 stop bit

Bit0

Bit1

Bit2

Bit3

Bit4

Bit5

Bit6

Bit7

Start

Bit

Next

Start

Bit

Possible

Parity

Bit

Data Frame

Next Data Frame

1 1/2 stop bits

a) 1 Stop Bit

b) 1 1/2 stop Bits

c) 2 Stop Bits

d) 1/2 Stop Bit

Loading...

Loading...