Controller area network (bxCAN) UM0306

296/519

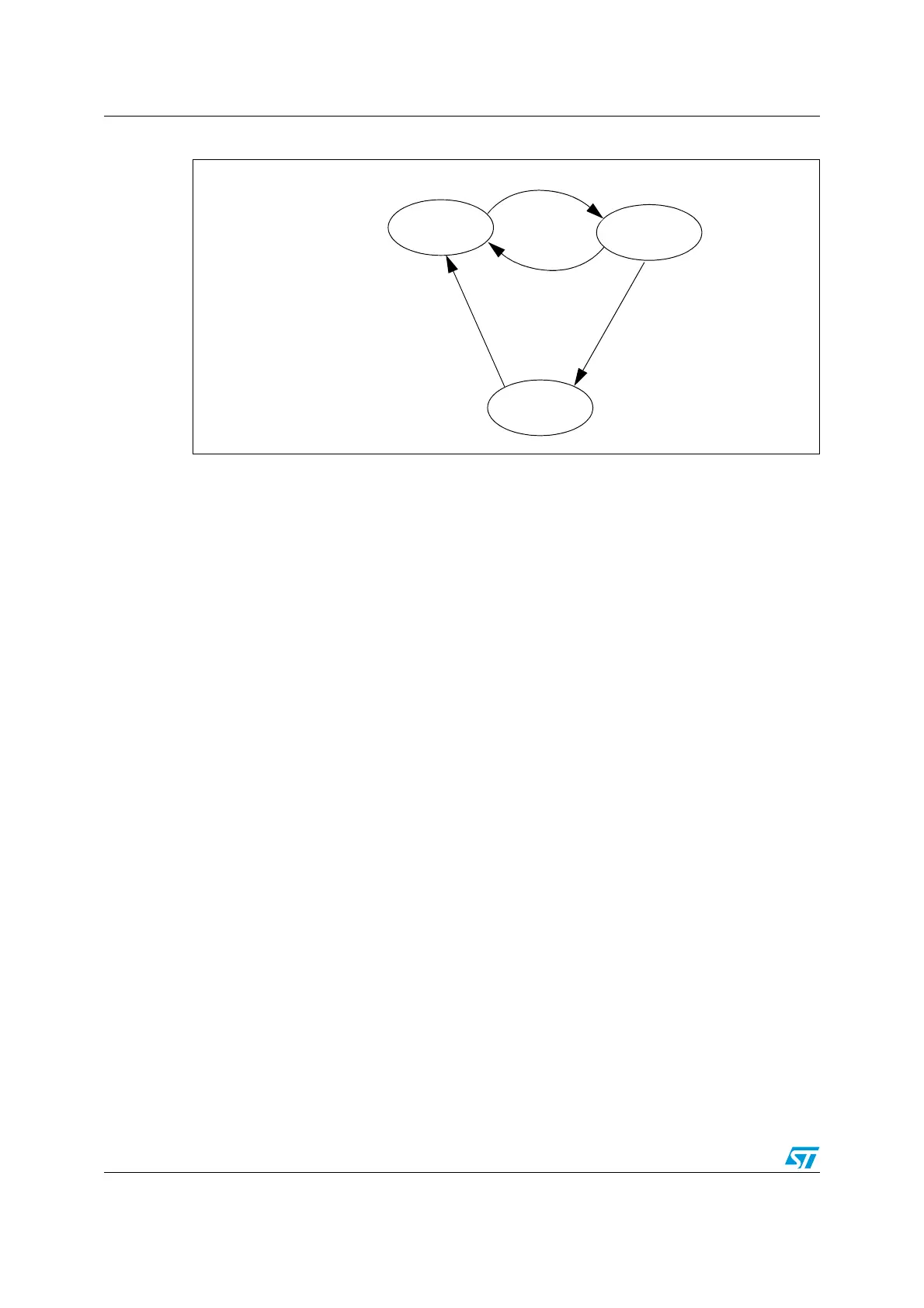

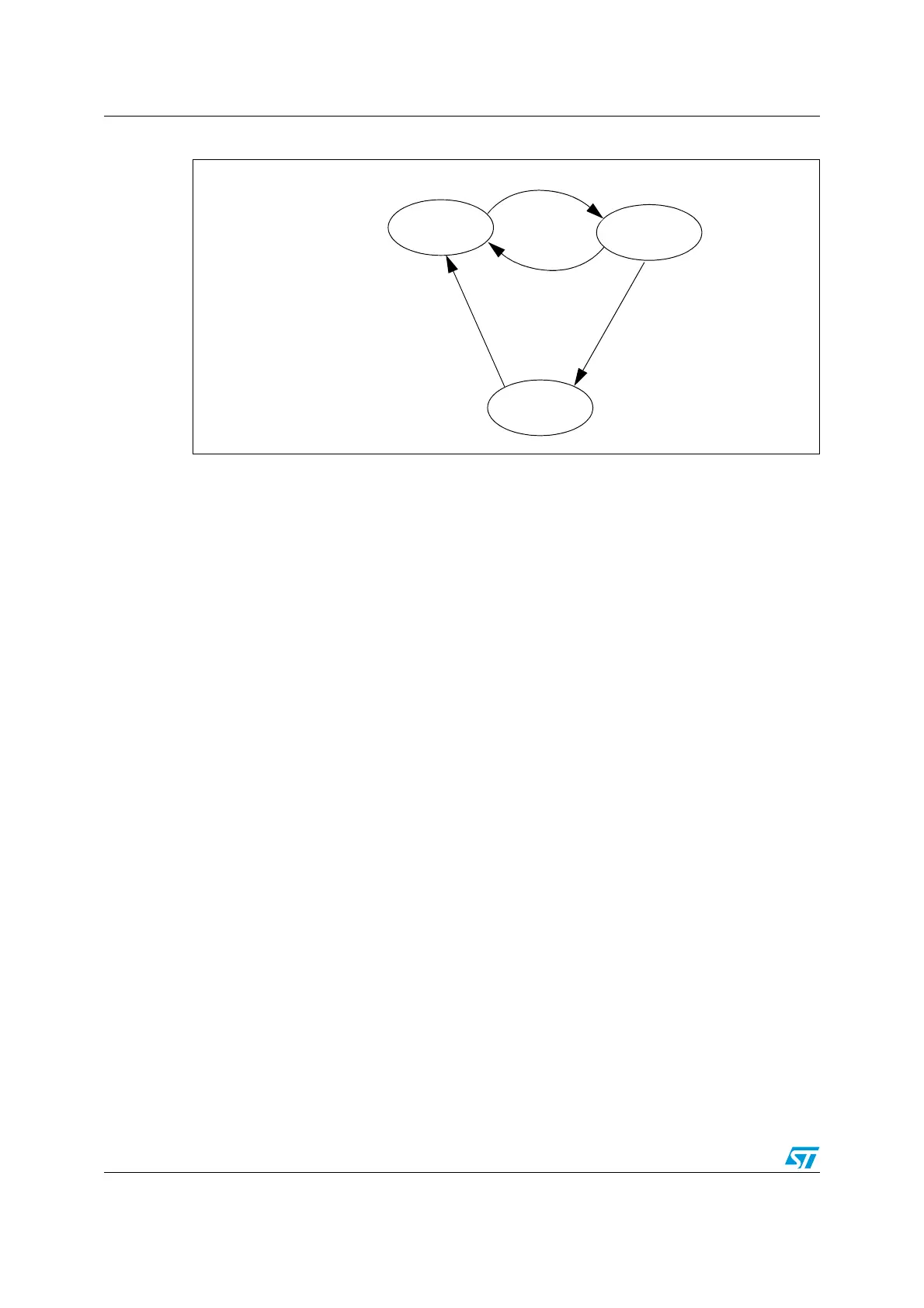

Figure 129. CAN error state diagram

14.5.6 Error management

The error management as described in the CAN protocol is handled entirely by hardware

using a Transmit Error Counter (TEC value, in CAN_ESR register) and a Receive Error

Counter (REC value, in the CAN_ESR register), which get incremented or decremented

according to the error condition. For detailed information about TEC and REC management,

please refer to the CAN standard.

Both of them may be read by software to determine the stability of the network.

Furthermore, the CAN hardware provides detailed information on the current error status in

CAN_ESR register. By means of the CAN_IER register (ERRIE bit, etc.), the software can

configure the interrupt generation on error detection in a very flexible way.

Bus-Off recovery

The Bus-Off state is reached when TEC is greater than 255, this state is indicated by BOFF

bit in CAN_ESR register. In Bus-Off state, the bxCAN is no longer able to transmit and

receive messages.

Depending on the ABOM bit in the CAN_MCR register bxCAN will recover from Bus-Off

(become error active again) either automatically or on software request. But in both cases

the bxCAN has to wait at least for the recovery sequence specified in the CAN standard

(128 occurrences of 11 consecutive recessive bits monitored on CANRX).

If ABOM is set, the bxCAN will start the recovering sequence automatically after it has

entered Bus-Off state.

If ABOM is cleared, the software must initiate the recovering sequence by requesting

bxCAN to enter and to leave initialization mode.

Note: In initialization mode, bxCAN does not monitor the CANRX signal, therefore it cannot

complete the recovery sequence. To recover, bxCAN must be in normal mode.

14.5.7 Bit timing

The bit timing logic monitors the serial bus-line and performs sampling and adjustment of

the sample point by synchronizing on the start-bit edge and resynchronizing on the following

edges.

ERROR PASSIVE

When TEC or REC > 127

When TEC and REC < 128,

ERROR ACTIVE

BUS OFF

When TEC > 255When 128 * 11 recessive bits occur:

Loading...

Loading...