Advanced control timer (TIM1) UM0306

156/519

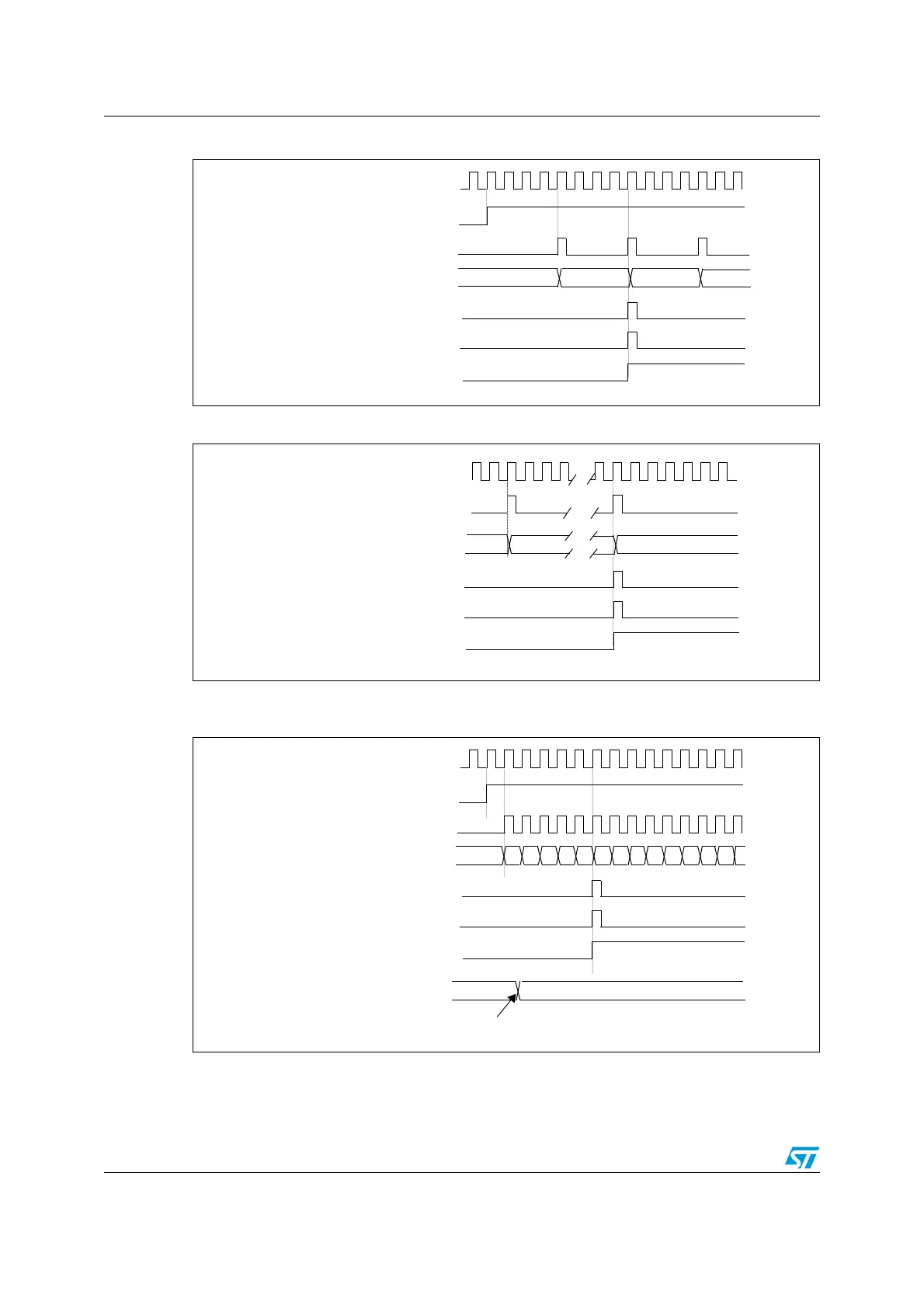

Figure 29. Counter timing diagram, internal clock divided by 4

Figure 30. Counter timing diagram, internal clock divided by N

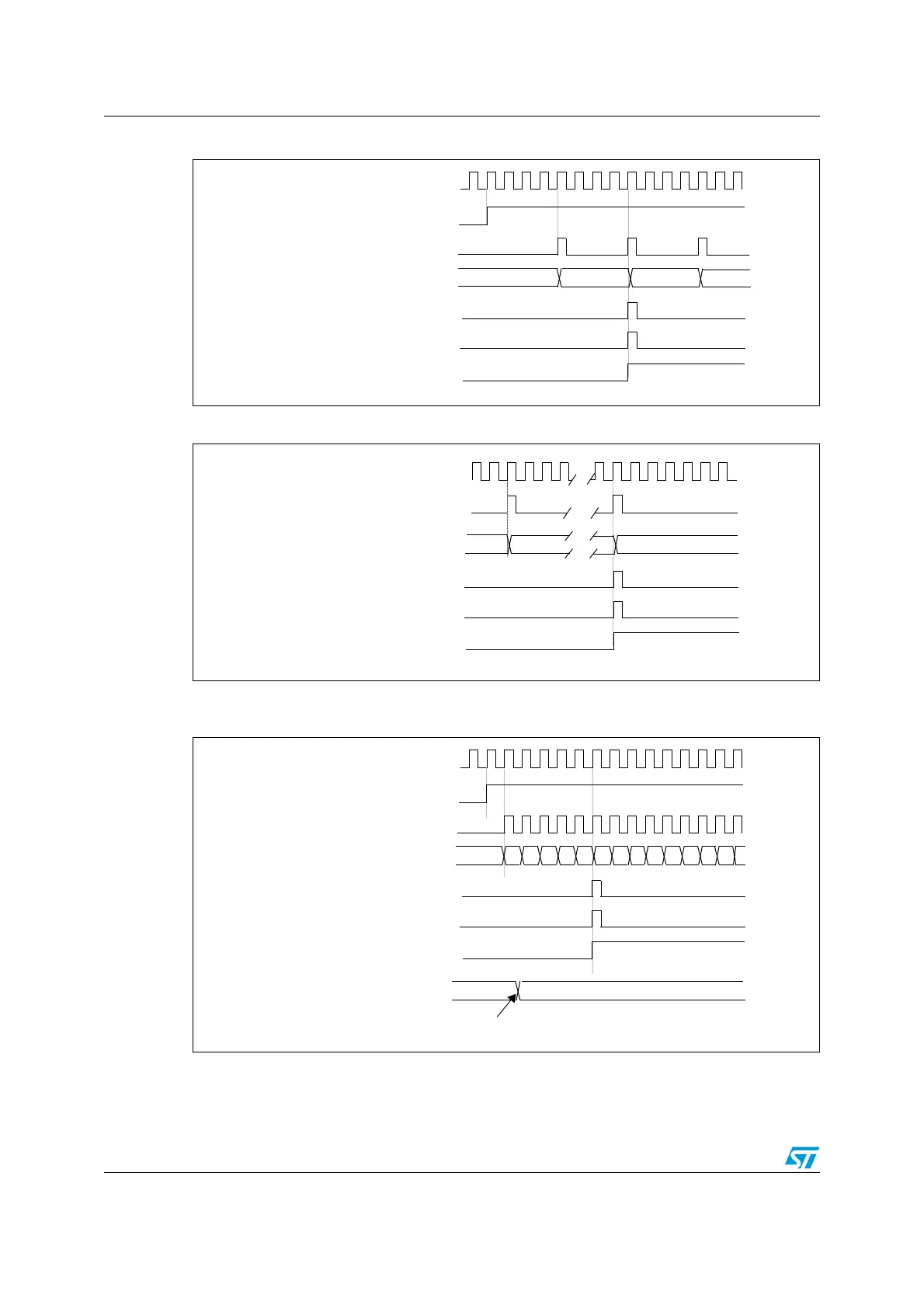

Figure 31. Counter timing diagram, Update event when ARPE=0 (TIM1_ARR not

preloaded)

CK_PSC

0000 0001

CNT_EN

TIMER CLOCK = CK_CNT

COUNTER REGISTER

UPDATE INTERRUPT FLAG (UIF)

0035

0036

COUNTER OVERFLOW

UPDATE EVENT (UEV)

TIMER CLOCK = CK_CNT

COUNTER REGISTER

00

1F

20

UPDATE INTERRUPT FLAG (UIF)

COUNTER OVERFLOW

UPDATE EVENT (UEV)

CK_PSC

CK_PSC

00

CNT_EN

TIMER CLOCK = CK_CNT

COUNTER REGISTER

UPDATE INTERRUPT FLAG (UIF)

COUNTER OVERFLOW

UPDATE EVENT (UEV)

01 02 03 04 05 06 0732 33 34 35 3631

AUTO-RELOAD REGISTER

FF 36

Write a new value in TIM1_ARR

Loading...

Loading...