Debug support (DBG) UM0306

502/519

The packets emitted by the ITM are output to the TPIU (Trace Port Interface Unit). The

formatter of the TPIU adds some extra packets (refer to TPIU) and then output the complete

packets sequence to the debugger host.

The bit TRCEN of the Debug Exception and Monitor Control Register must be enabled

before you program or use the ITM.

20.14.2 Timestamp packets, synchronization and overflow packets

Timestamp packets encode timestamp information, generic control and synchronization. It

uses a 21-bit timestamp counter (with possible prescalers) which is reset at each time

stamp packet emission. This counter can be either clocked by the CPU clock or the SWV

clock.

A synchronization packet consists of 6 bytes equal to 0x80_00_00_00_00_00 which is

emitted to the TPIU as 00 00 00 00 00 80 (LSB emitted first).

A synchronization packet is a timestamp packet control. It is emitted at each DWT trigger.

For this, the DWT must be configured to trigger the ITM: the bit CYCCNTENA (bit0) of the

DWT Control Register must be set. In addition, the bit2 (SYNCENA) of the ITM Trace

Control Register must be set.

Note: If the SYNENA bit is not set, the DWT generates Synchronization triggers to the TPIU which

will send only TPIU synchronization packets and not ITM synchronization packets.

An overflow packet consists is a special timestamp packets which indicates that data has

been written but the FIFO was full.

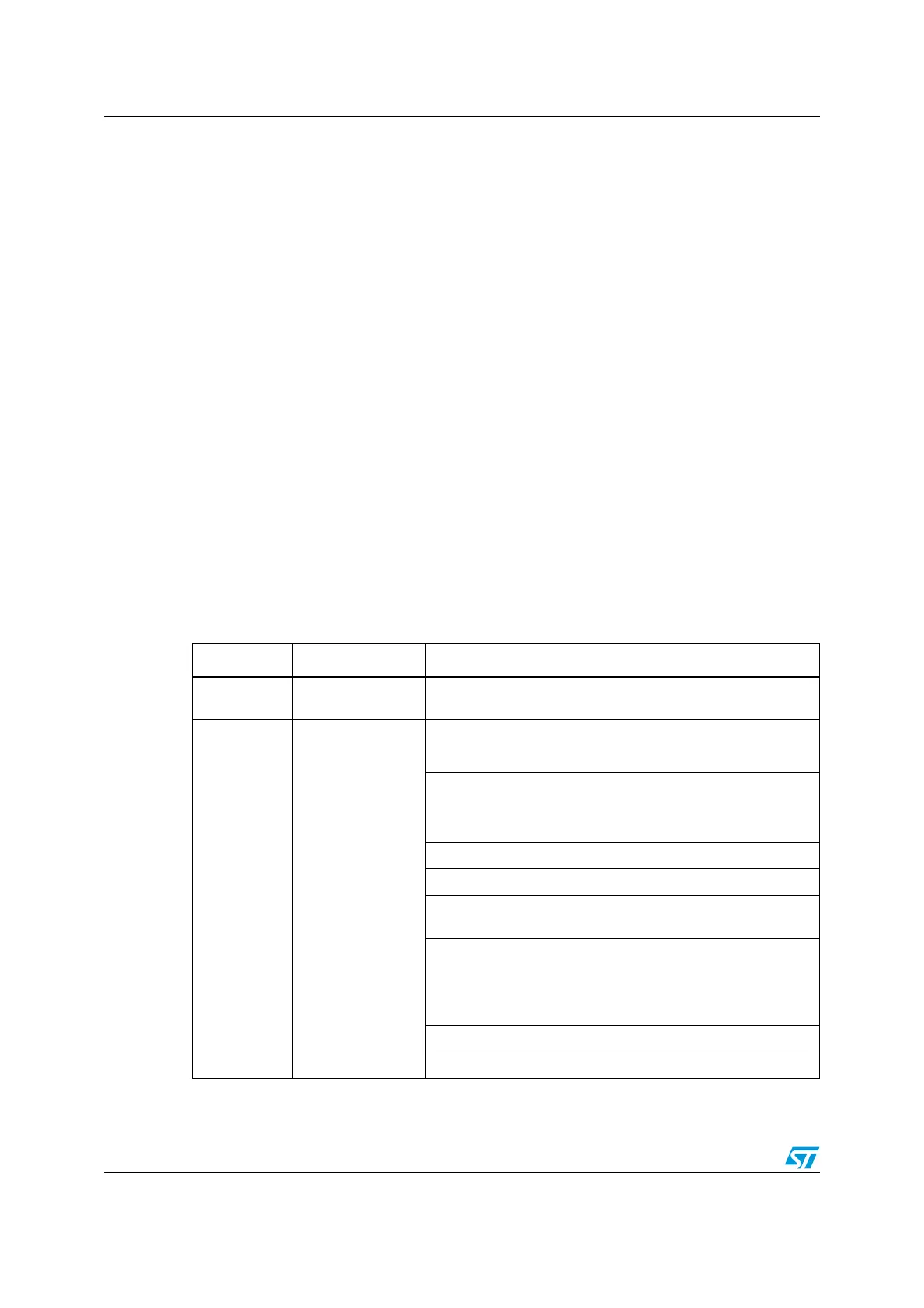

Table 77. Main ITM registers

Address Register Details

@E0000FB0 ITM Lock Access

Write 0xC5ACCE55 to unlock Write Access to the other ITM

registers

@E0000E80 ITM Trace Control

Bits 31-24 = Always 0

Bits 23 = BUSY

Bits 22-16 = 7-bits ATB ID which identifies the source of the

trace data.

Bits 15-10 = Always 0

Bits 9:8 = TSPrescale = Time Stamp Prescaler

Bits 7-5 = Reserved

Bit 4 = SWOENA = Enable SWV behavior (to clock the

timestamp counter by the SWV clock).

Bit 3 = DWTENA: Enable the DWT Stimulus

Bit 2 = SYNCENA: this bit must be to 1 to enable the DWT to

generate synchronization triggers so that the TPIU can then

emit the synchronization packets.

Bit 1 = TSENA (Timestamp Enable)

Bit 0 = ITMENA: Global Enable Bit of the ITM

Loading...

Loading...