UM0306 Debug support (DBG)

503/519

Example of configuration

To output a simple value to the TPIU:

● Configure the TPIU and enable the I/IO_TRACEN to assign TRACE I/Os in the MCU

● Write 0xC5ACCE55 to the ITM Lock Access Register to unlock the write access to the

ITM registers

● Write 0x00010005 to the ITM Trace Control Register to enable the ITM with Sync

enabled and an ATB ID different from 0x00

● Write 0x1 to the ITM Trace Enable Register to enable the Stimulus Port 0

● Write 0x1 to the ITM Trace Privilege Register to unmask stimulus ports 7:0

● Write the value to output in the Stimulus Port Register 0: this can be done by software

(using a printf function)

20.15 MCU debug component (MCUDBG)

The MCU debug component helps the debugger provide support for:

● Low-power modes

● Clock control for timers, watchdog and bxCAN during a breakpoint

● Control of the trace pins assignment

20.15.1 Debug support for low-power modes

To enter low-power mode, the instruction WFI or WFE must be executed.

The MCU implements several low-power modes which can either deactivate the CPU clock

or reduce the power of the CPU.

The core does not allow FCLK or HCLK to be turned off during a debug session. As these

are required for the debugger connection, during a debug, they must remain active. The

MCU integrates special means to allow the user to debug software in low-power modes.

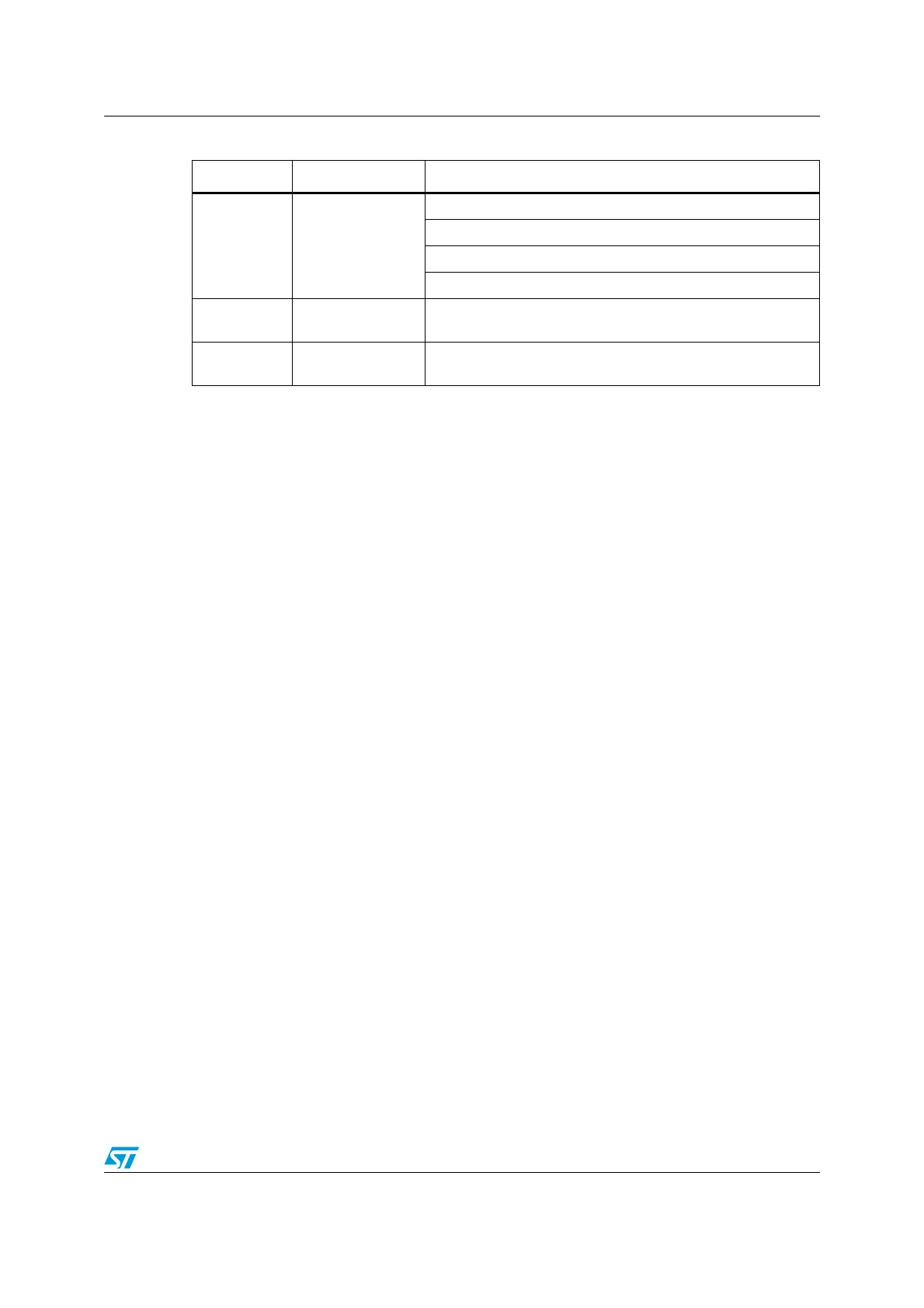

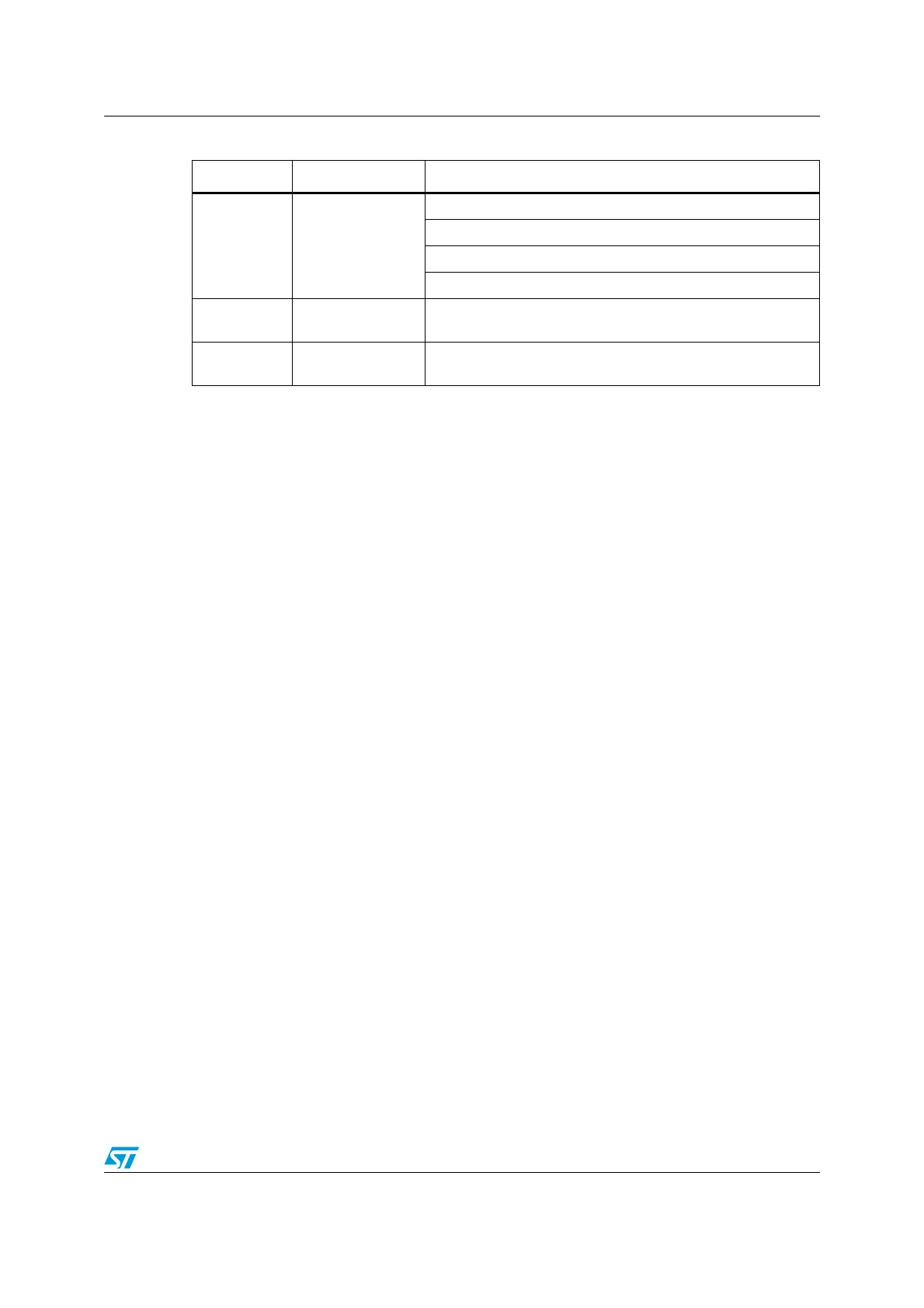

@E0000E40 ITM Trace Privilege

Bit 3: mask to enable tracing ports31:24

Bit 2: mask to enable tracing ports23:16

Bit 1: mask to enable tracing ports15:8

Bit 0: mask to enable tracing ports7:0

@E0000E00 ITM Trace Enable

Each bit enables the corresponding Stimulus port to generate

trace.

@E0000000-

E000007C

Stimulus Port

Registers 0-31

Write the 32-bits data on the selected Stimulus Port (32

available) to be traced out.

Table 77. Main ITM registers

Address Register Details

Loading...

Loading...