UM0306 Window watchdog (WWDG)

145/519

11 Window watchdog (WWDG)

11.1 Introduction

The Window Watchdog is used to detect the occurrence of a software fault, usually

generated by external interference or by unforeseen logical conditions, which causes the

application program to abandon its normal sequence. The Watchdog circuit generates an

MCU reset on expiry of a programmed time period, unless the program refreshes the

contents of the downcounter before the T6 bit becomes cleared. An MCU reset is also

generated if the 7-bit downcounter value (in the control register) is refreshed before the

downcounter has reached the window register value. This implies that the counter must be

refreshed in a limited window.

11.2 Main features

● Programmable free-running downcounter

● Conditional reset

– Reset (if watchdog activated) when the downcounter value becomes less than 40h

– Reset (if watchdog activated) if the downcounter is reloaded outside the window

(see Figure 23)

11.3 Functional description

If the watchdog is activated (the WDGA bit is set in the WWDG_CR register) and when the

7-bit downcounter (T[6:0] bits) rolls over from 40h to 3Fh (T6 becomes cleared), it initiates a

reset. If the software reloads the counter while the counter is greater than the value stored in

the window register, then a reset is generated.

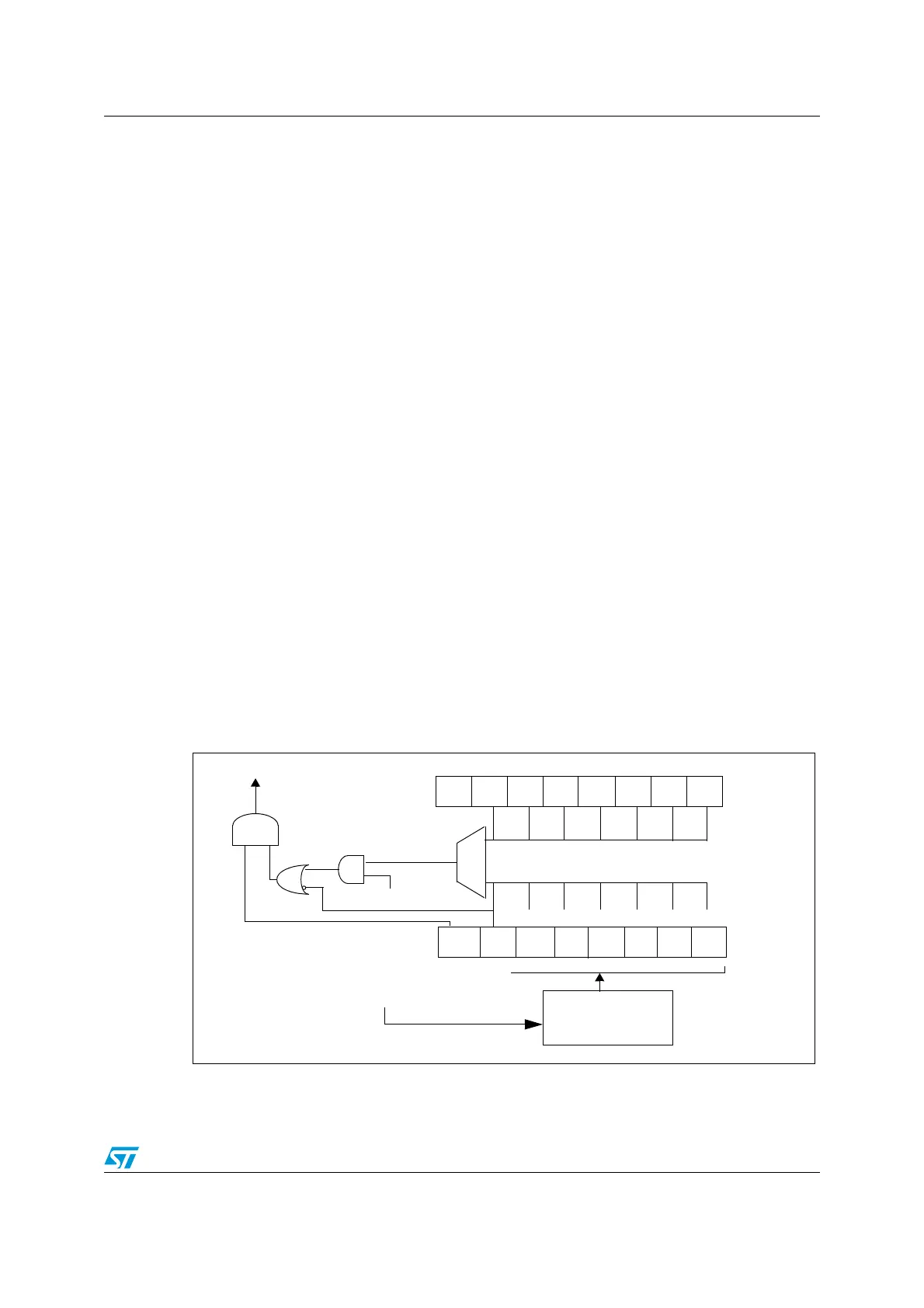

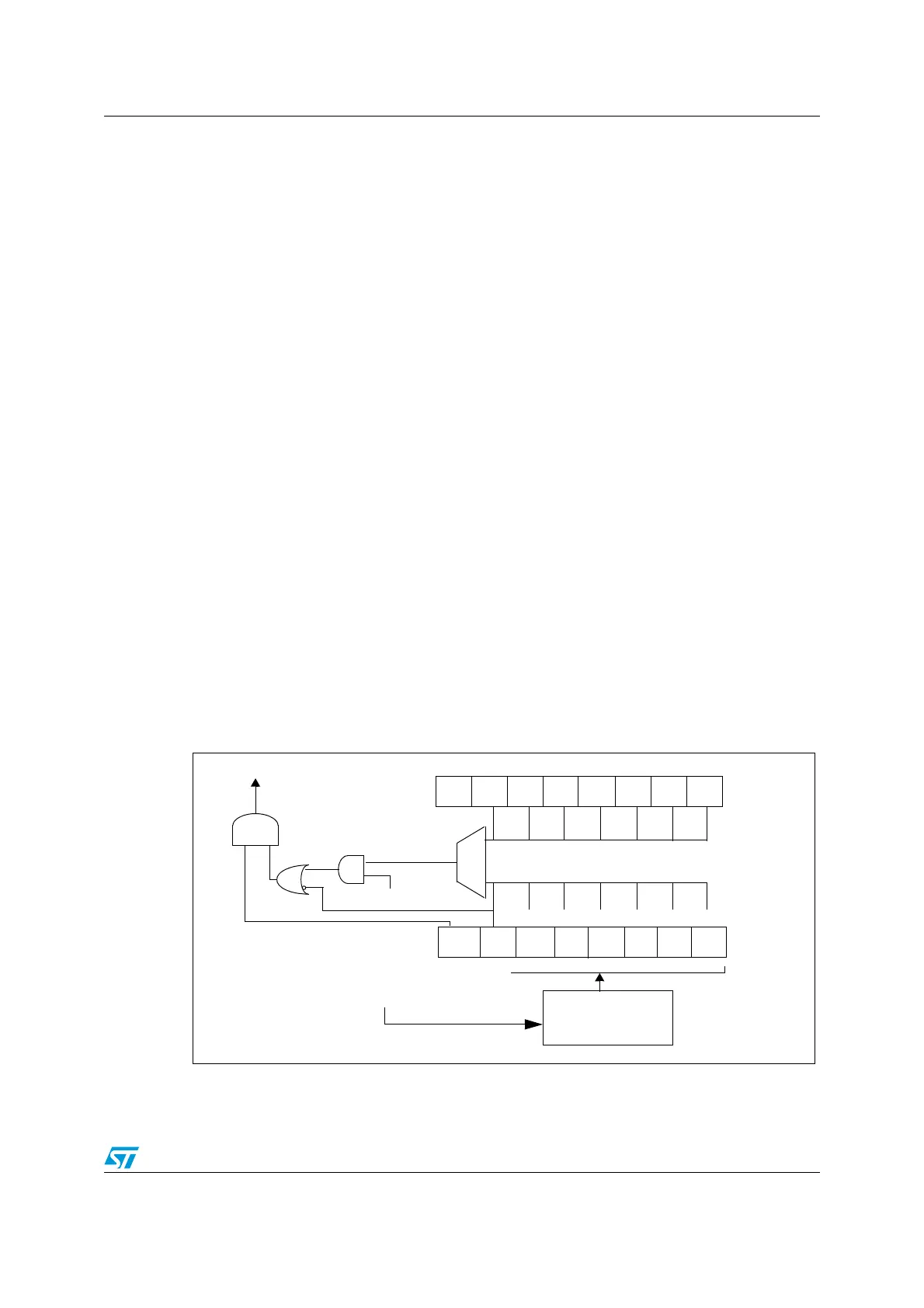

Figure 22. Watchdog block diagram

The application program must write in the WWDG_CR register at regular intervals during

normal operation to prevent an MCU reset. This operation must occur only when the counter

RESET

WDGA

6-BIT DOWNCOUNTER (CNT)

T6

WATCHDOG CONTROL REGISTER (WWDG_CR)

T1

T2

T3

T4

T5

-

W6

W0

WATCHDOG CONFIGURATION REGISTER (WWDG_CFR)

W1

W2

W3

W4

W5

comparator

T6:0 > W6:0

CMP

= 1 when

Write WWDG_CR

WDG PRESCALER

(WDGTB)

PCLK1

T0

(from RCC clock controller)

Loading...

Loading...