Real-Time Clock (RTC) UM0306

126/519

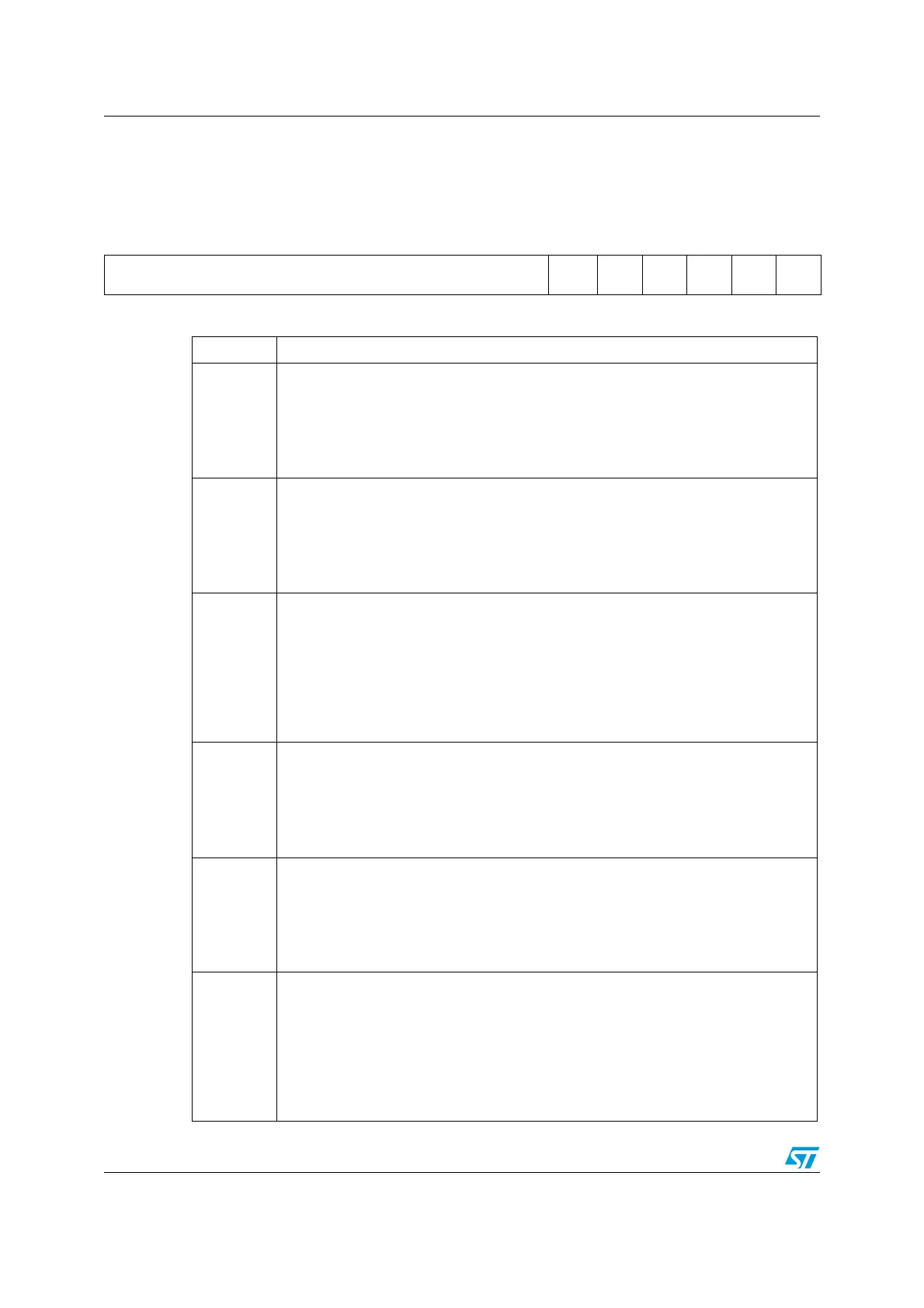

8.4.2 RTC control register low (RTC_CRL)

Address Offset: 04h

Reset value: 0020h

1514131211109876 5 43210

Reserved RTOFF CNF RSF OWF ALRF SECF

r rw rc_w0 rc_w0 rc_w0 rc_w0

Bits 15:6 Reserved, forced by hardware to 0.

Bit 5

RTOFF: RTC operation OFF

With this bit the RTC reports the status of the last write operation performed on its

registers, indicating if it has been completed or not. If its value is ‘0’ then it is not

possible to write to any of the RTC registers. This bit is read only.

0: Last write operation on RTC registers is still ongoing.

1: Last write operation on RTC registers terminated.

Bit 4

CNF: Configuration Flag

This bit must be set by software to enter in configuration mode so as to allow new

values to be written in the RTC_CNT, RTC_ALR or RTC_PRL registers. The write

operation is only executed when the CNF bit is reset by software after has been set.

0: Exit configuration mode (start update of RTC registers).

1: Enter configuration mode.

Bit 3

RSF: Registers Synchronized Flag

This bit is set by hardware at each time the RTC_CNT and RTC_DIV registers are

updated and cleared by software. Before any read operation after an APB1 reset or

an APB1 clock stop, this bit must be cleared by software, and the user application

must wait until it is set to be sure that the RTC_CNT, RTC_ALR or RTC_PRL

registers are synchronized.

0: Registers not yet synchronized.

1: Registers synchronized.

Bit 2

OWF: OverfloW Flag

This bit is set by hardware when the 32-bit programmable counter overflows. An

interrupt is generated if OWIE=1 in the RTC_CRH register. It can be cleared only by

software. Writing ‘1’ has no effect.

0: Overflow not detected

1: 32-bit programmable counter overflow occurred.

Bit 1

ALRF: Alarm Flag

This bit is set by hardware when the 32-bit programmable counter reaches the

threshold set in the RTC_ALR register. An interrupt is generated if ALRIE=1 in the

RTC_CRH register. It can be cleared only by software. Writing ‘1’ has no effect.

0: Alarm not detected

1: Alarm detected

Bit 0

SECF: Second Flag

This bit is set by hardware when the 32-bit programmable prescaler overflows, thus

incrementing the RTC counter. Hence this flag provides a periodic signal with a

period corresponding to the resolution programmed for the RTC counter (usually

one second). An interrupt is generated if SECIE=1 in the RTC_CRH register. It can

be cleared only by software. Writing ‘1’ has no effect.

0: Second flag condition not met.

1: Second flag condition met.

Loading...

Loading...