UM0306 Advanced control timer (TIM1)

219/519

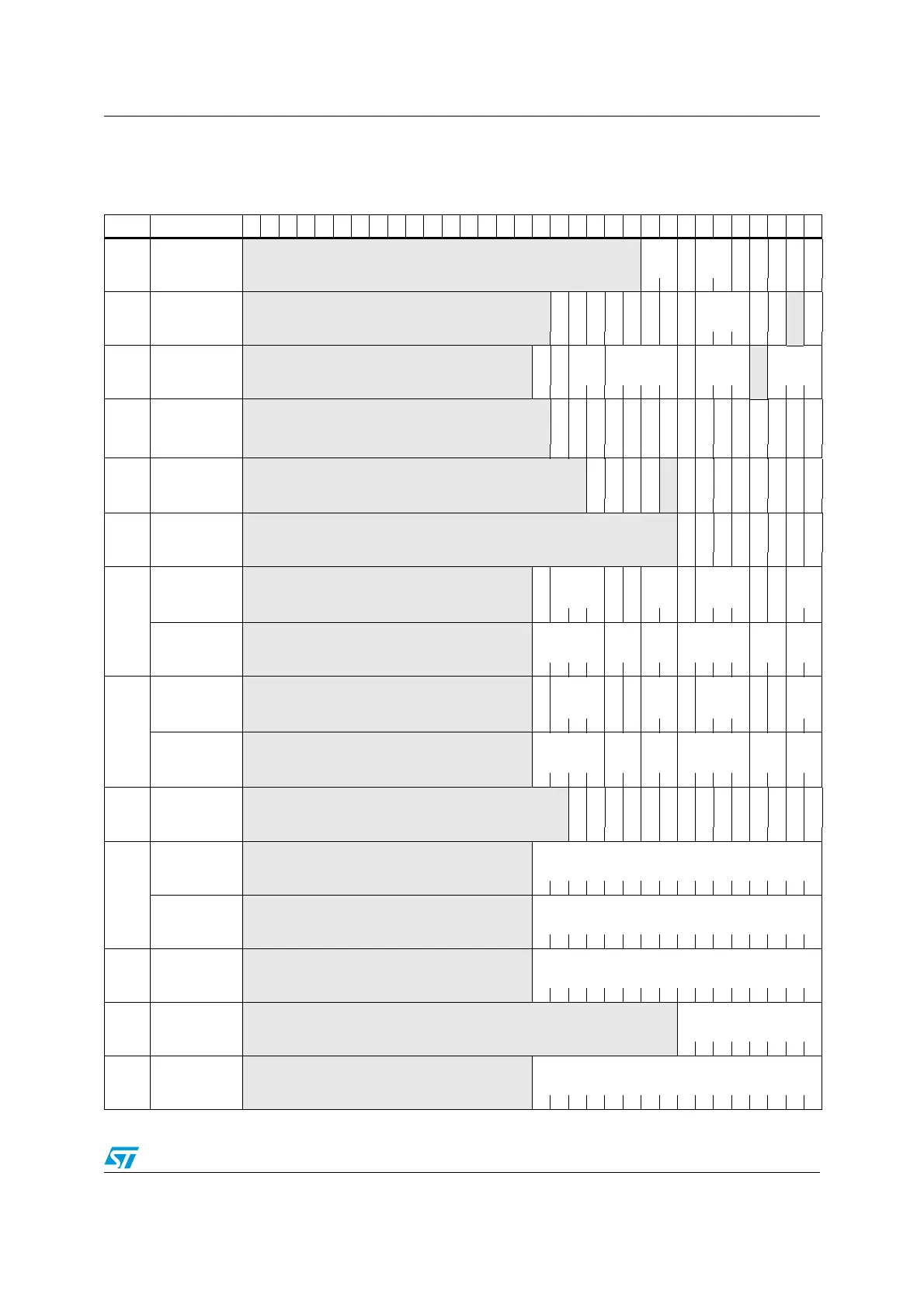

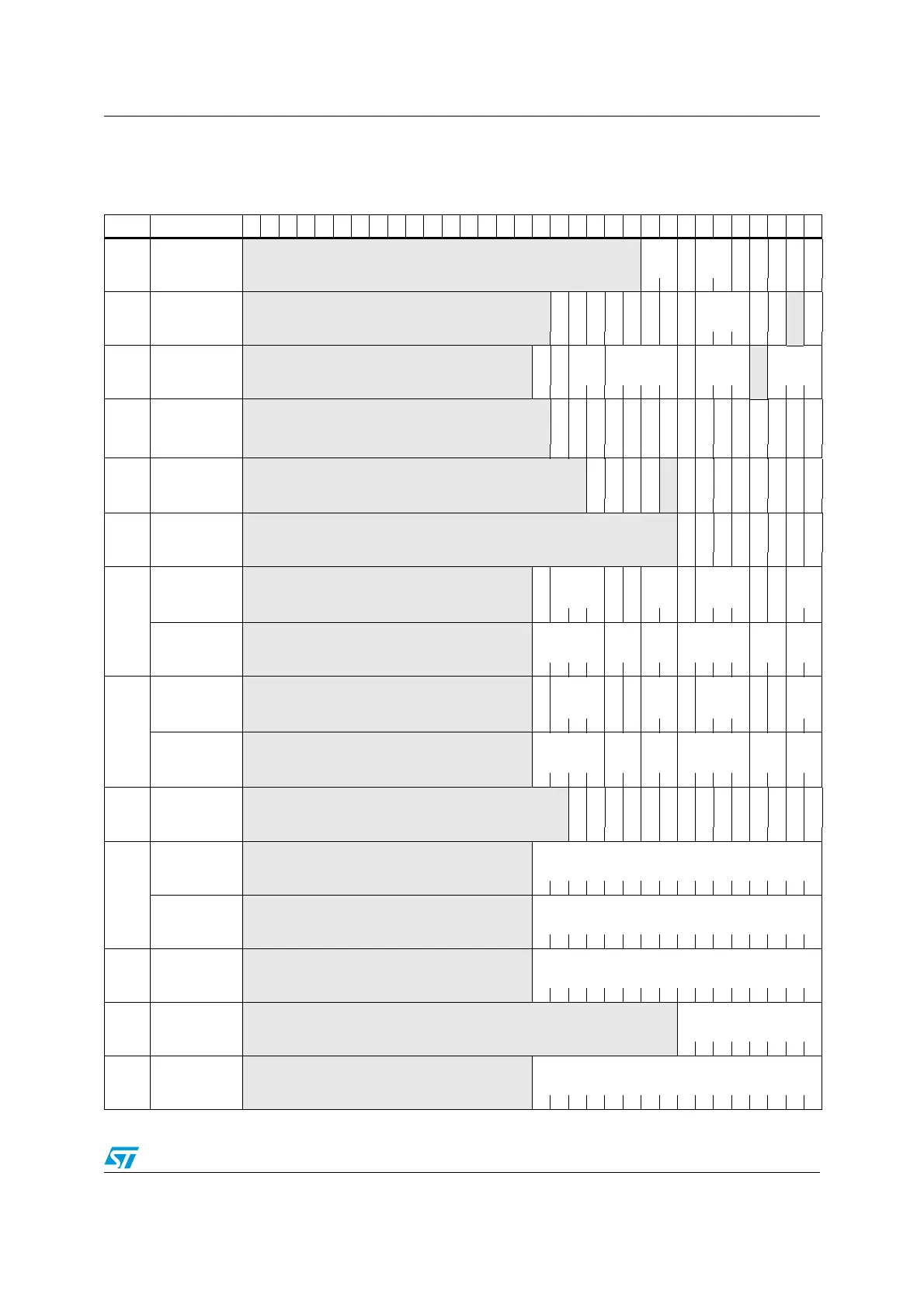

12.6 TIM1 register map

TIM1 registers are mapped as 16-bit addressable registers as described in the table below:

Table 38. TIM1 - Register Map and Reset Values

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

00h

TIM1_CR1

Reserved

CKD

[1:0]

ARPE

CMS

[1:0]

DIR

OPM

URS

UDIS

CEN

Reset Value 0000000000

04h

TIM1_CR2

Reserved

OIS4

OIS3N

OIS3

OIS2N

OIS2

OIS1N

OIS1

TI1S

MMS[2:0]

CCDS

CCUS

Reserved

CCPC

Reset Value 0000000000000 0

08h

TIM1_SMCR

Reserved

ETP

ECE

ETPS

[1:0]

ETF[3:0]

MSM

TS[2:0]

Reserved

SMS[2:0]

Reset Value 000000000000 000

0Ch

TIM1_DIER

Reserved

TDE

COMDE

CC4DE

CC3DE

CC2DE

CC1DE

UDE

BIE

TIE

COMIE

CC4IE

CC3IE

CC2IE

CC1IE

UIE

Reset Value 000000000000000

10h

TIM1_SR

Reserved

CC4OF

CC3OF

CC2OF

CC1OF

Reserved

BIF

TIF

COMIF

CC4IF

CC3IF

CC2IF

CC1IF

UIF

Reset Value 0000 00000000

14h

TIM1_EGR

Reserved

BG

TG

COM

CC4G

CC3G

CC2G

CC1G

UG

Reset Value 00000000

18h

TIM1_CCMR1

Output Compare

mode

Reserved

OC2CE

OC2M

[2:0]

OC2PE

OC2FE

CC2S

[1:0]

OC1CE

OC1M

[2:0]

OC1PE

OC1FE

CC1S

[1:0]

Reset Value 0000000000000000

TIM1_CCMR1

Input Capture

mode

Reserved

IC2F[3:0]

IC2

PSC

[1:0]

CC2S

[1:0]

IC1F[3:0]

IC1

PSC

[1:0]

CC1S

[1:0]

Reset Value 0000000000000000

1Ch

TIM1_CCMR2

Output Compare

mode

Reserved

O24CE

OC4M

[2:0]

OC4PE

OC4FE

CC4S

[1:0]

OC3CE

OC3M

[2:0]

OC3PE

OC3FE

CC3S

[1:0]

Reset Value 0000000000000000

TIM1_CCMR2

Input Capture

mode

Reserved

IC4F[3:0]

IC4

PSC

[1:0]

CC4S

[1:0]

IC3F[3:0]

IC3

PSC

[1:0]

CC3S

[1:0]

Reset Value 0000000000000000

20h

TIM1_CCER

Reserved

CC4P

CC4E

CC3NP

CC3NE

CC3P

CC3E

CC2NP

CC2NE

CC2P

CC2E

CC1NP

CC1NE

CC1P

CC1E

Reset Value 00000000000000

24h

TIM1_CNT

Reserved

CNT[15:0]

Reset Value 0000000000000000

28h

TIM1_PSC

Reserved

PSC[15:0]

Reset Value 0000000000000000

2Ch

TIM1_ARR

Reserved

ARR[15:0]

Reset Value 0000000000000000

30h

TIM1_RCR

Reserved

REP[7:0]

Reset Value 00000000

34h

TIM1_CCR1

Reserved

CCR1[15:0]

Reset Value 0000000000000000

Loading...

Loading...