UM0306 General purpose and alternate function I/O (GPIO and AFIO)

87/519

5.3 Alternate function I/O and debug configuration (AFIO)

To optimize the number of peripherals available for the 64-pin or the 100-pin package, it is

possible to remap some alternate functions to some other pins. This is achieved by

software, by programming the AF remap and debug I/O configuration register

(AFIO_MAPR) on page 92. In this case, the alternate functions are no longer mapped to

their original assignations.

5.3.1 Using OSC_IN/OSC_OUT pins as GPIO ports PD0/PD1

The external oscillator pins OSC_IN/OSC_OUT can be used as general purpose I/O

PD0/PD1 by programming the PD01_REMAP bit in the AF remap and debug I/O

configuration register (AFIO_MAPR).

5.3.2 BXCAN alternate function remapping

The BXCAN signal can be mapped on Port A, Port B or Port E as shown in Tabl e 13.

5.3.3 JTAG/SWD alternate function remapping

The debug interface signals are mapped on the GPIO ports as shown in Tabl e 14.

To optimize the number of free GPIOs during debugging, this mapping can be configured in

different ways by programming the SWJ_CFG[1:0] bits in the AF remap and debug I/O

configuration register (AFIO_MAPR). Refer to Tabl e 1 5

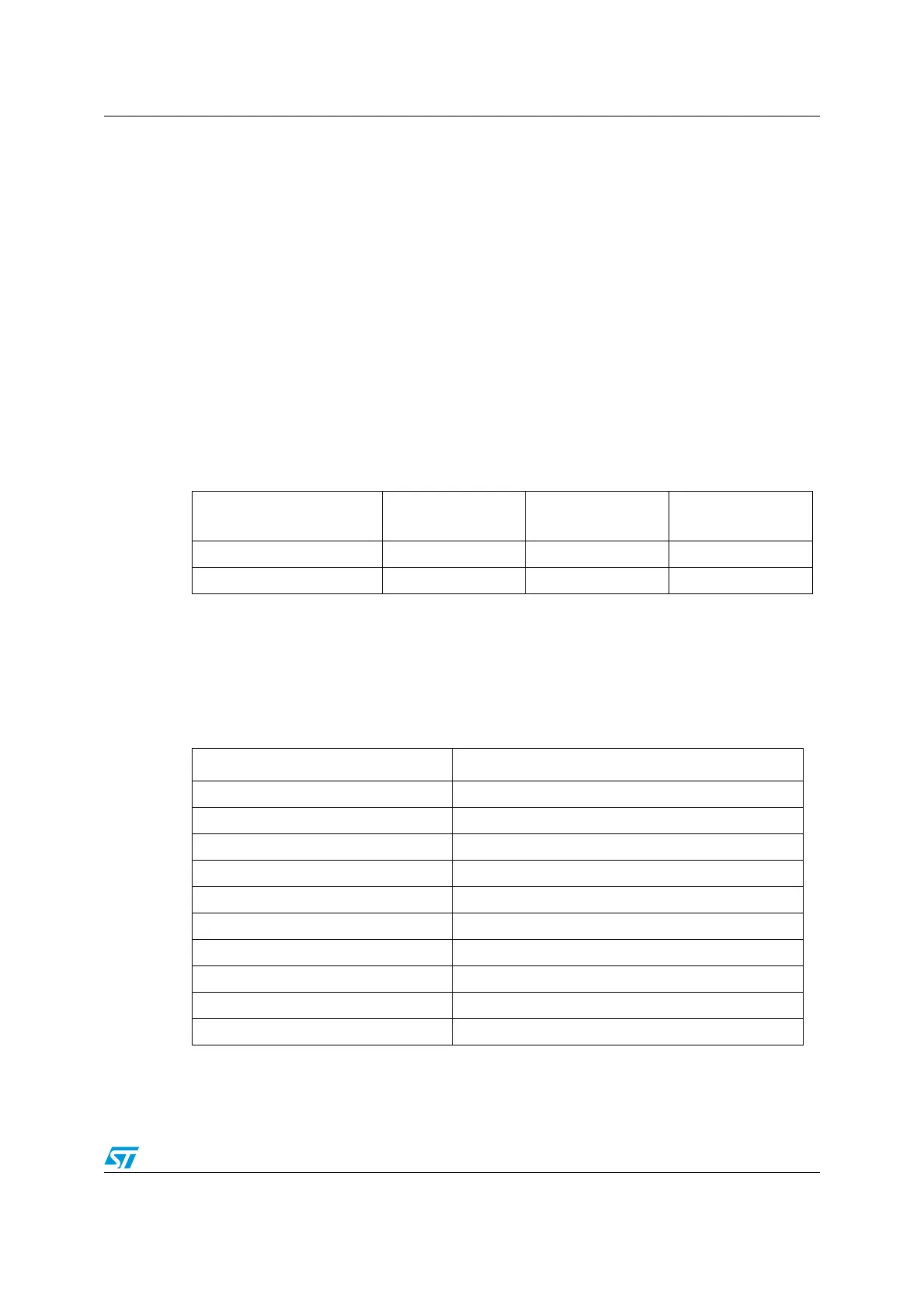

Table 13. BXCAN alternate function remapping

Alternate Function

CAN_REMAP[1:0] =

“00”

CAN_REMAP[1:0] =

“10”

(1)

1. Remap not available on 36-pin package

CAN_REMAP[1:0] =

“11”

(2)

2. Remap available only on 100-pin package

CANRX PA11 PB8 PD0

CANTX PA12 PB9 PD1

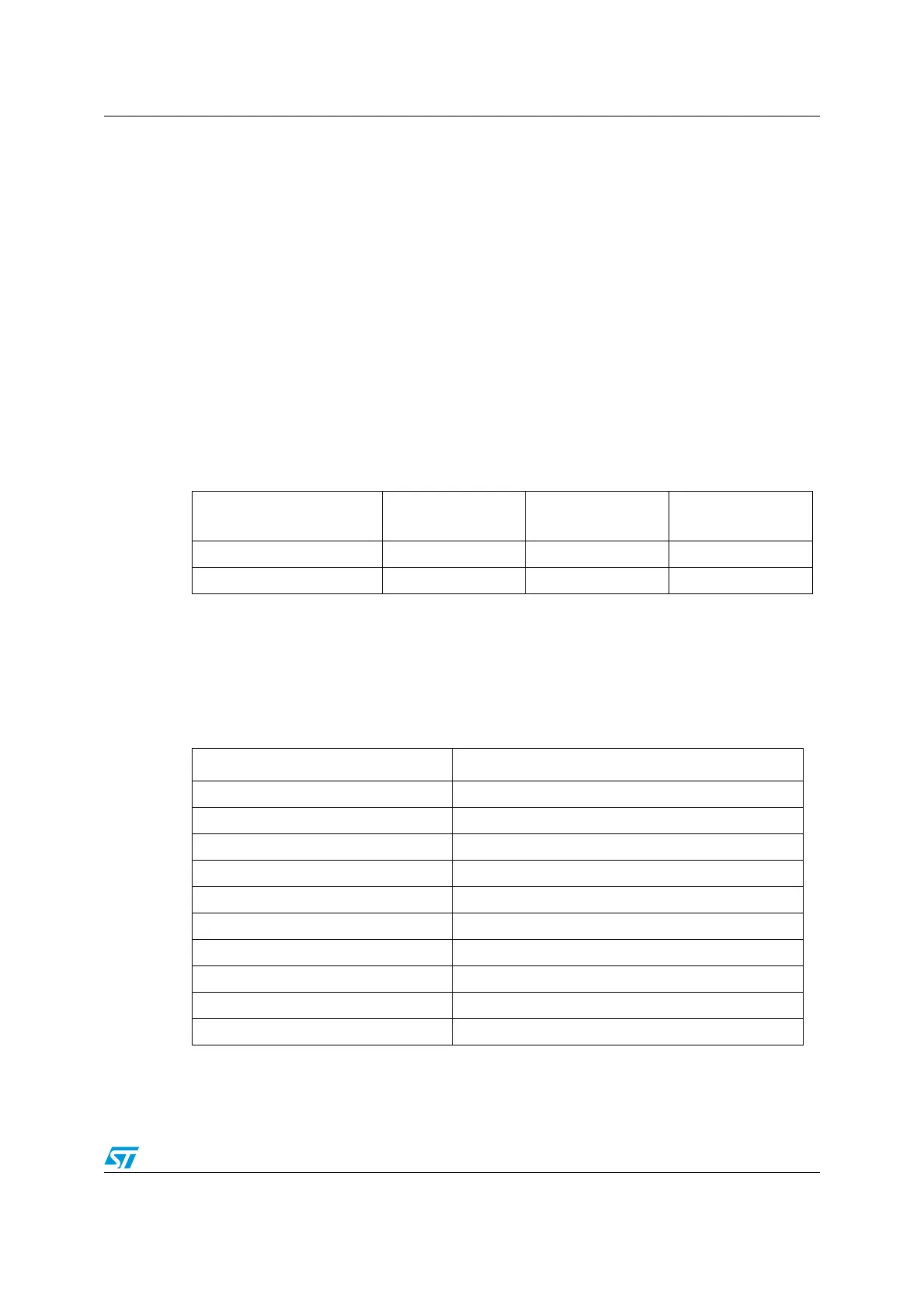

Table 14. Debug interface signals

Alternate function GPIO port

JTMS / SWDIO PA13

JTCK / SWCLK PA14

JTDI PA15

JTDO / TRACESWO PB3

JNTRST PB4

TRACECK PE2

TRACED0 PE3

TRACED1 PE4

TRACED2 PE5

TRACED3 PE6

Loading...

Loading...