Memory and bus architecture UM0306

28/519

2.3.2 Embedded SRAM

The STM32F10x features 20 KBytes of static SRAM. It can be accessed as bytes, half-

words (16 bits) or full words (32 bits). The SRAM start address is 0x2000 0000.

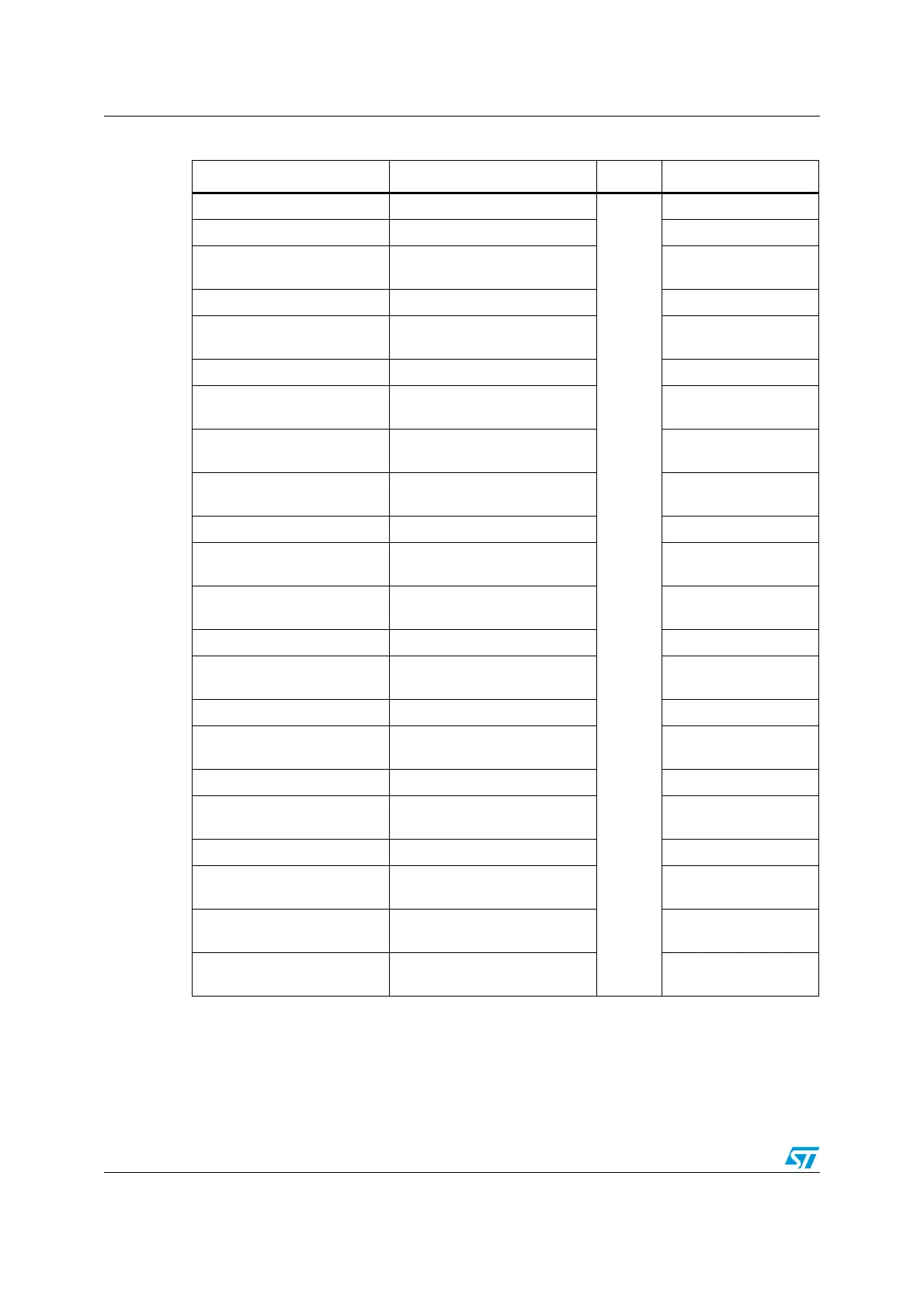

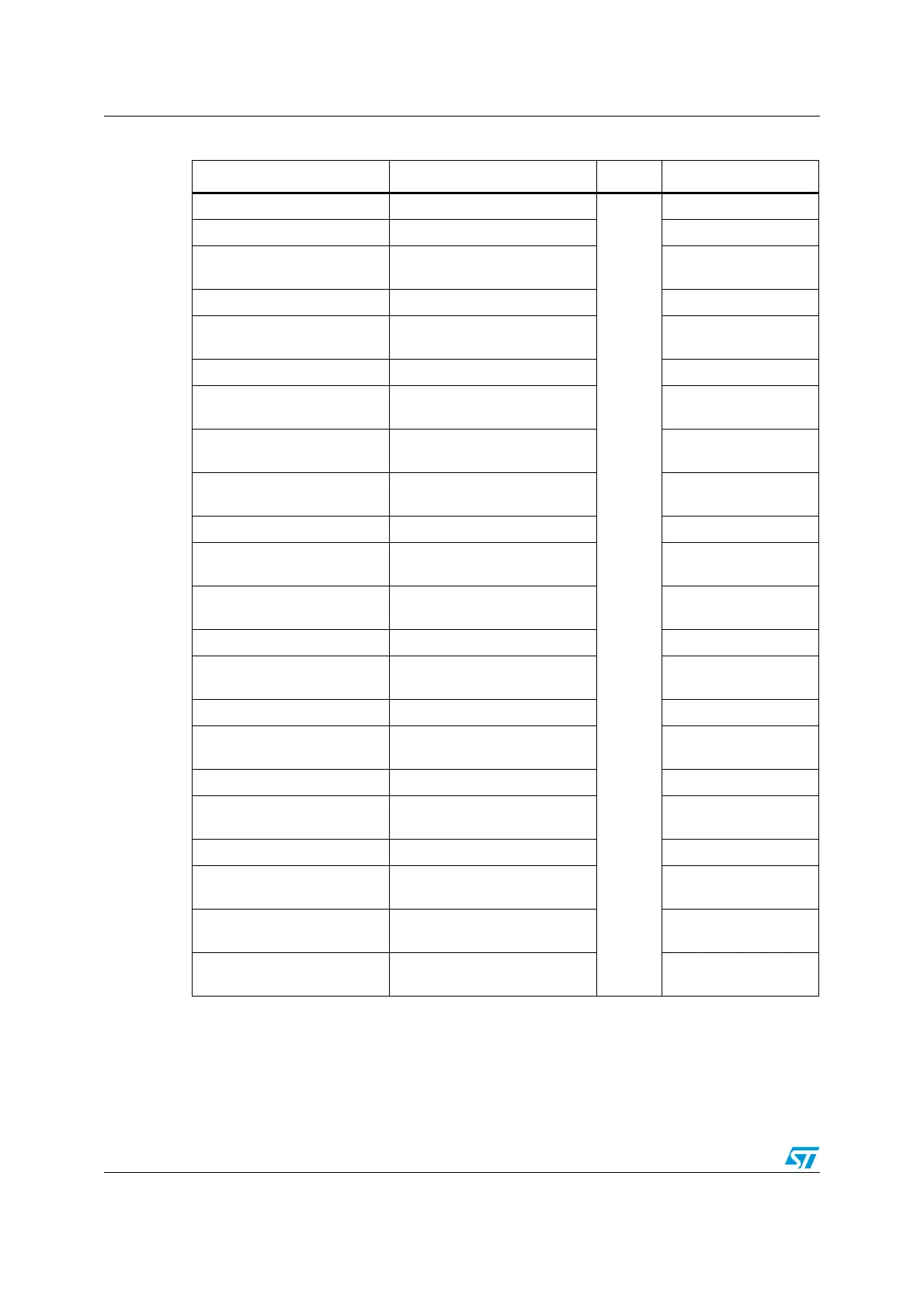

0x4000 8000 - 0x4000 77FF Reserved

APB1

0x4000 7000 - 0x4000 73FF Power control PWR Section 3.5 on page 44

0x4000 6C00 - 0x4000 6FFF Backup registers (BKP)

Section 9.6 on page

137

0x4000 6800 - 0x4000 6BFF Reserved

0x4000 6400 - 0x4000 67FF bxCAN

Section 14.9 on page

324

0x4000 6000 - 0x4000 63FF USB SRAM 256 x 16-bit

0x4000 5C00 - 0x4000 5FFF USB Registers

Section 18.7 on page

450

0x4000 5800 - 0x4000 5BFF I2C2

Section 15.7 on page

358

0x4000 5400 - 0x4000 57FF I2C1

Section 15.7 on page

358

0x4000 5000 - 0x4000 4FFF Reserved

0x4000 4800 - 0x4000 4BFF USART3

Section 17.5 on page

418

0x4000 4400 - 0x4000 47FF USART2

Section 17.5 on page

418

0x4000 4000 - 0x4000 3FFF Reserved

0x4000 3800 - 0x4000 3BFF SPI2

Section 16.5 on page

376

0x4000 3400 - 0x4000 37FF Reserved

0x4000 3000 - 0x4000 33FF Independent watchdog (IWDG)

Section 10.3 on page

144

0x4000 2C00 - 0x4000 2FFF Window watchdog (WWDG)

0x4000 2800 - 0x4000 2BFF RTC

Section 8.5 on page

132

0x4000 2400 - 0x4000 0FFF Reserved

0x4000 0800 - 0x4000 0BFF TIM4 timer

Section 13.6 on page

280

0x4000 0400 - 0x4000 07FF TIM3 timer

Section 13.6 on page

280

0x4000 0000 - 0x4000 03FF TIM2 timer

Section 13.6 on page

280

Table 1. Register boundary addresses (continued)

Boundary Address Peripheral Bus Register Map

Loading...

Loading...