General purpose timer (TIMx) UM0306

252/519

selection blocks.

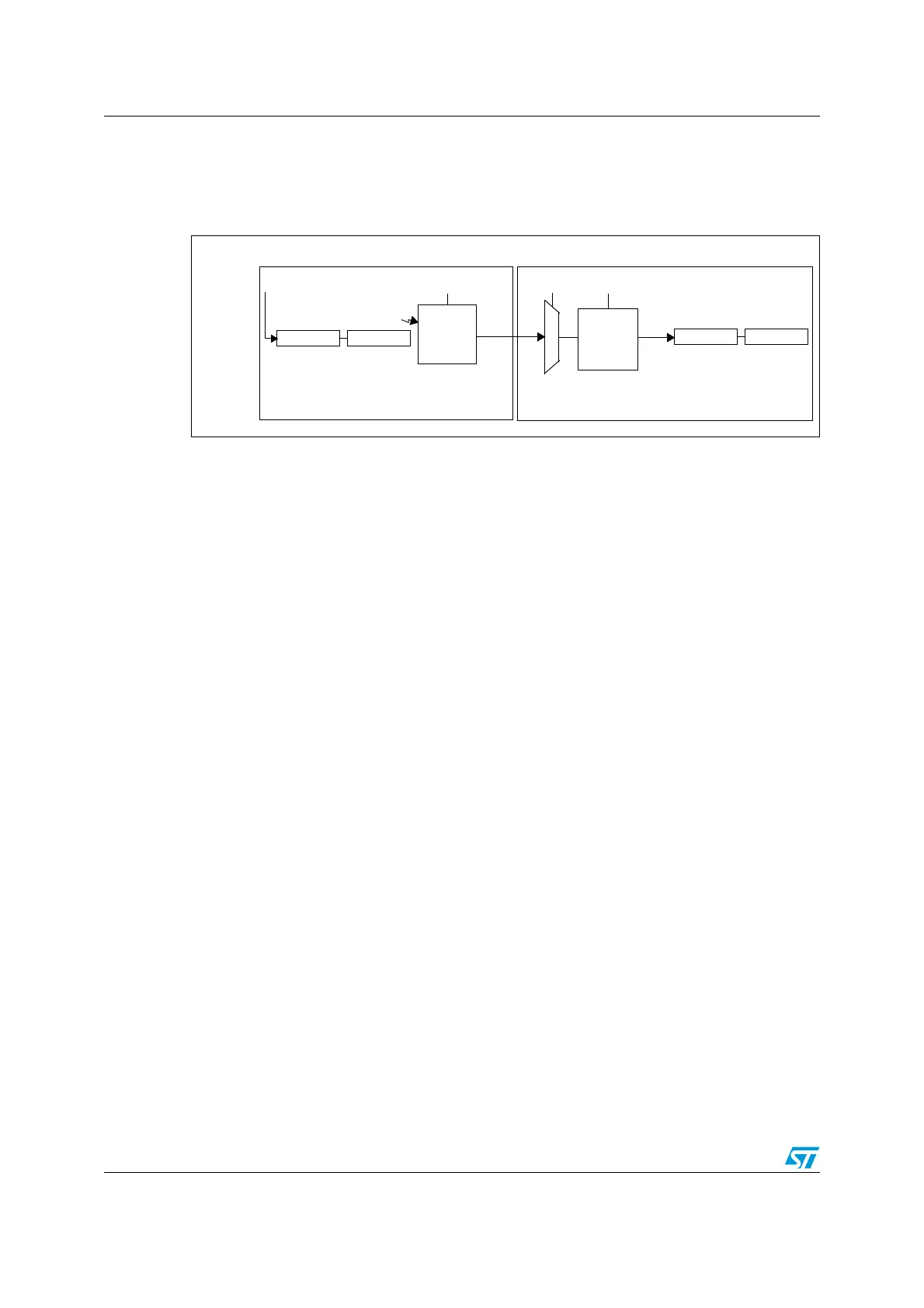

Using one timer as prescaler for the another

Figure 112. Master/Slave timer example

For example, you can configure Timer 1 to act as a prescaler for Timer 2. Refer to

Figure 112. To do this:

● Configure Timer 1 in master mode so that it outputs a periodic trigger signal on each

update event UEV. If you write MMS=010 in the TIM1_CR2 register, a rising edge is

output on TRGO1 each time an update event is generated.

● To connect the TRGO1 output of Timer 1 to Timer 2, Timer 2 must be configured in

slave mode using ITR1 as internal trigger. You select this through the TS bits in the

TIM2_SMCR register (writing TS=001).

● Then you put the slave mode controller in external clock mode 1 (write SMS=111 in the

TIM2_SMCR register). This causes Timer 2 to be clocked by the rising edge of the

periodic Timer 1 trigger signal (which correspond to the timer 1 counter overflow).

● Finally both timers must be enabled by setting their respective CEN bits (TIMx_CR1

register).

Note: If OCx is selected on Timer 1 as trigger output (MMS=1xx), its rising edge is used to clock

the counter of timer 2.

Using one timer to enable another timer

In this example, we control the enable of Timer 2 with the output compare 1 of Timer 1.

Refer to Figure 112 for connections. Timer 2 counts on the divided internal clock only when

OC1REF of Timer 1 is high. Both counter clock frequencies are divided by 3 by the

prescaler compared to CK_INT (f

CK_CNT

= f

CK_INT

/3).

● Configure Timer 1 master mode to send its Output Compare 1 Reference (OC1REF)

signal as trigger output (MMS=100 in the TIM1_CR2 register).

● Configure the Timer 1 OC1REF waveform (TIM1_CCMR1 register).

● Configure Timer 2 to get the input trigger from Timer 1 (TS=001 in the TIM2_SMCR

register).

● Configure Timer 2 in gated mode (SMS=101 in TIM2_SMCR register).

● Enable Timer 2 by writing ‘1’ in the CEN bit (TIM2_CR1 register).

● Start Timer 1 by writing ‘1’ in the CEN bit (TIM1_CR1 register).

Note: The counter 2 clock is not synchronized with counter 1, this mode only affects the Timer 2

counter enable signal.

TRGO1

UEV

ITR1

PRESCALER

COUNTER

SMSTSMMS

TIMER 1 TIMER 2

MASTER

MODE

CONTROL

SLAVE

MODE

CONTROL

CK_PSC

PRESCALER

COUNTER

Clock

INPUT

SELECTION

TRIGGER

Loading...

Loading...