Window watchdog (WWDG) UM0306

148/519

11.6 Register description

Refer to Section 1.1 on page 23 for a list of abbreviations used in register descriptions.

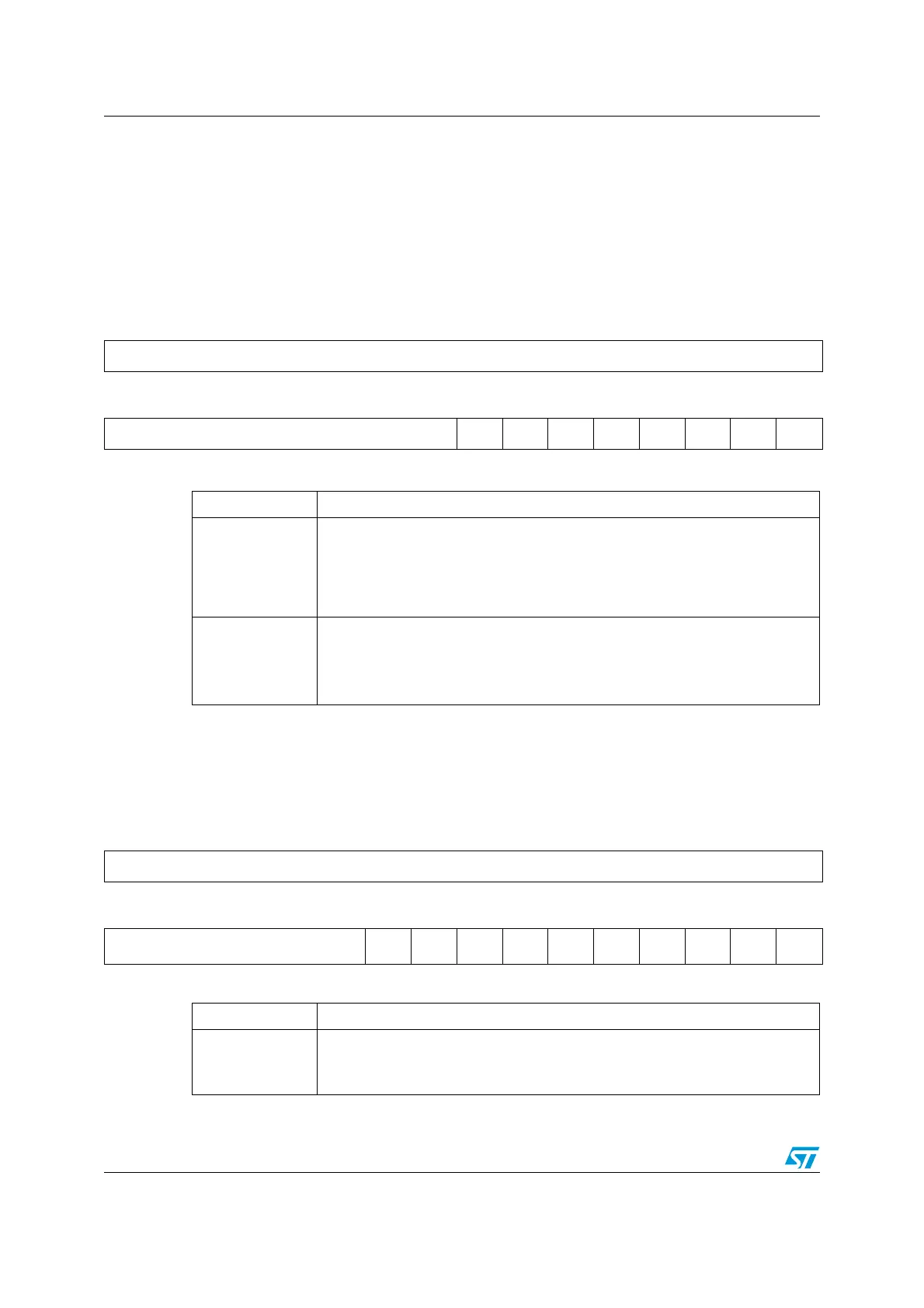

11.6.1 Control Register (WWDG_CR)

Address Offset: 00h

Reset Value: 0111 1111 (7Fh)

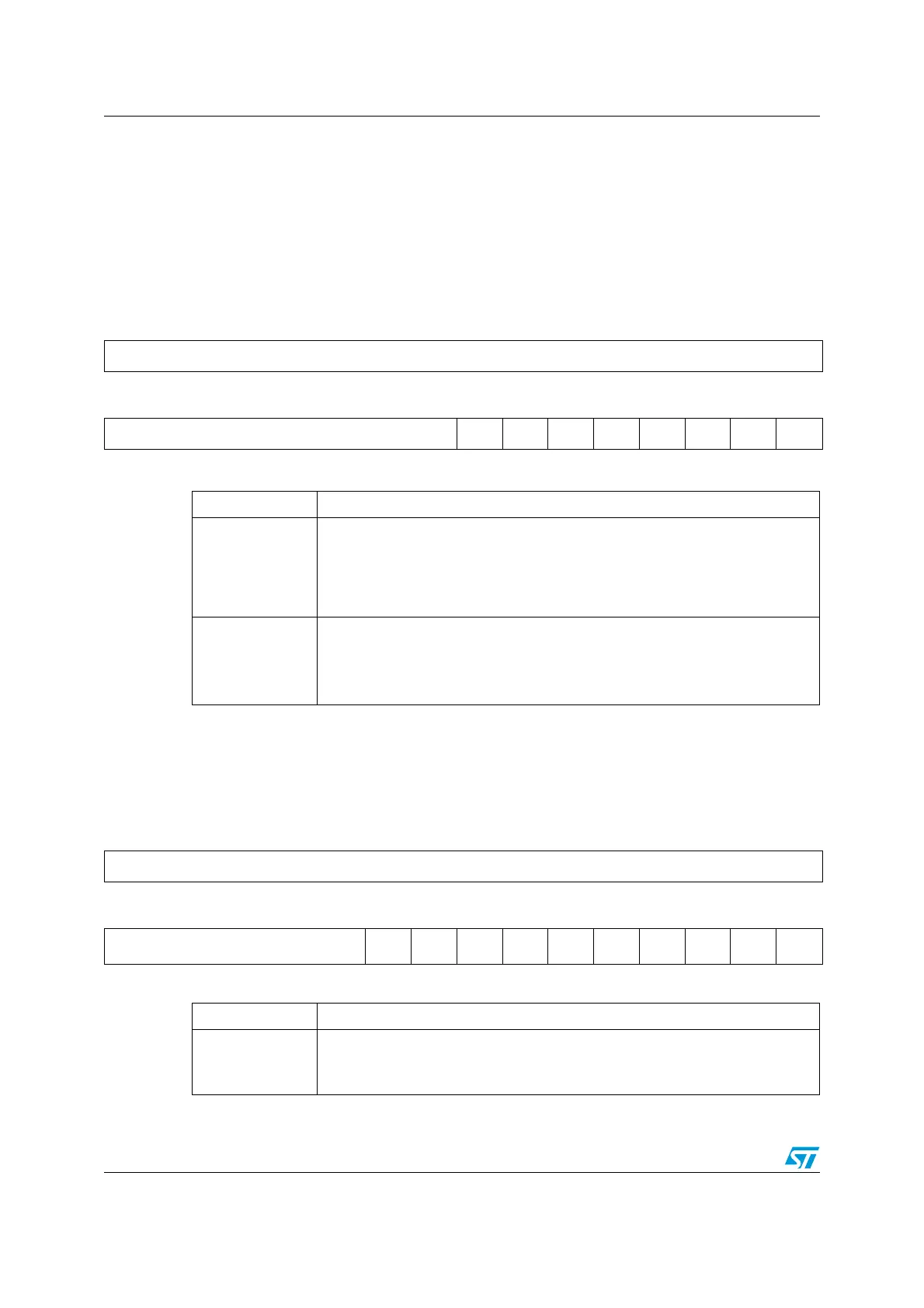

11.6.2 Configuration register (WWDG_CFR)

Address Offset: 04h

Reset Value: 0111 1111 (7Fh)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved WDGA T6 T5 T4 T3 T2 T1 T0

rs rw rw rw rw rw rw rw

Bits 31:8 Reserved

Bit 7

WDGA:

Activation bit

This bit is set by software and only cleared by hardware after a reset. When

WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

Bits 6:0

T[6:0]: 7-bit counter (MSB to LSB).

These bits contain the value of the watchdog counter. It is decremented every

(4096 x 2

WDGTB

) PCLK1 cycles. A reset is produced when it rolls over from 40h

to 3Fh (T6 becomes cleared).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved EWI

WDG

TB1

WDG

TB0

W6 W5 W4 W3 W2 W1 W0

rs rw rw rw rw rw rw rw rw rw

Bit 31:10 Reserved

Bit 9

EWI: Early Wakeup Interrupt

When set, an interrupt occurs whenever the counter reaches the value 40h.

This interrupt is only cleared by hardware after a reset.

Loading...

Loading...