UM0306 Advanced control timer (TIM1)

167/519

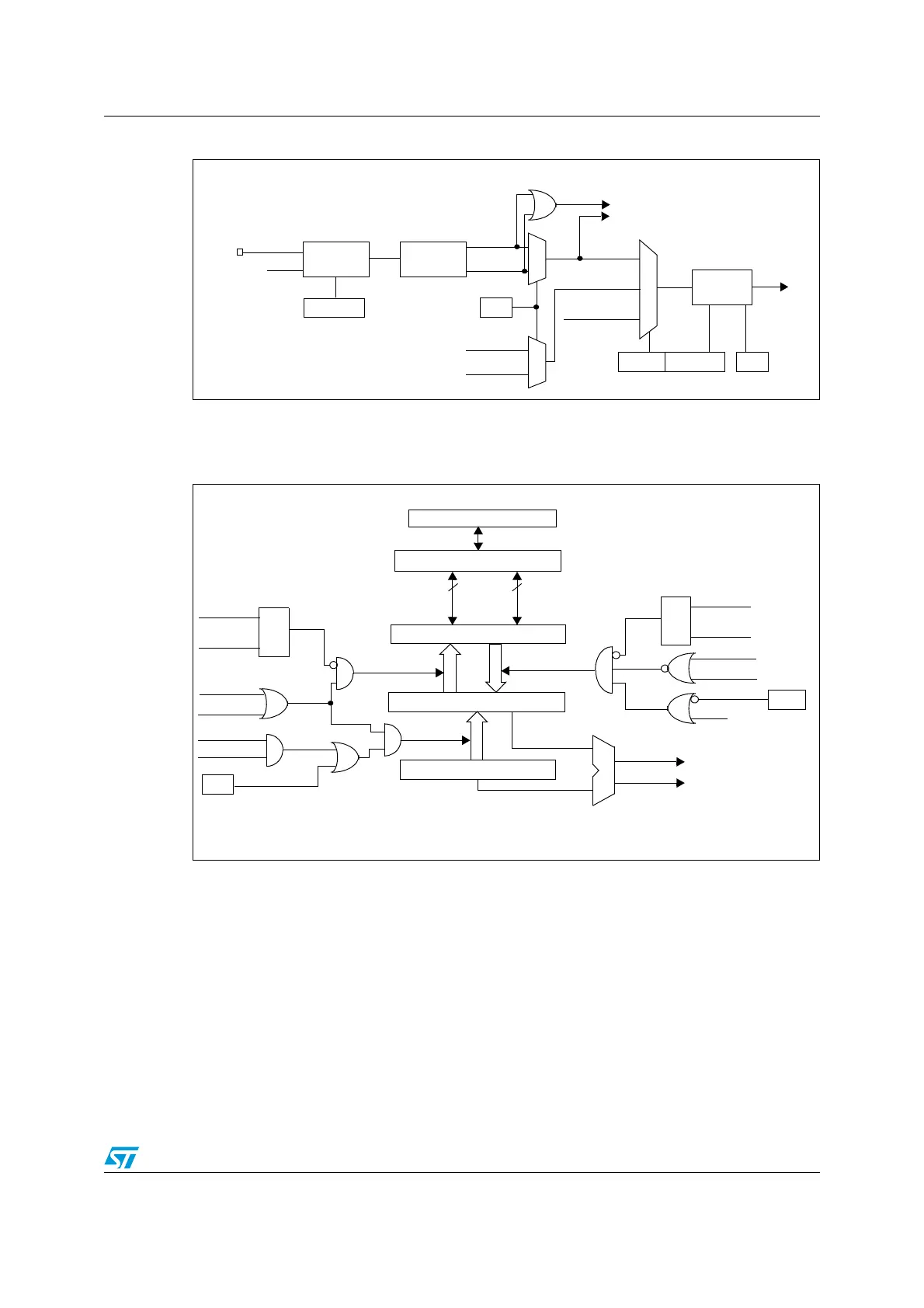

Figure 50. Capture/compare channel (example: channel 1 input stage)

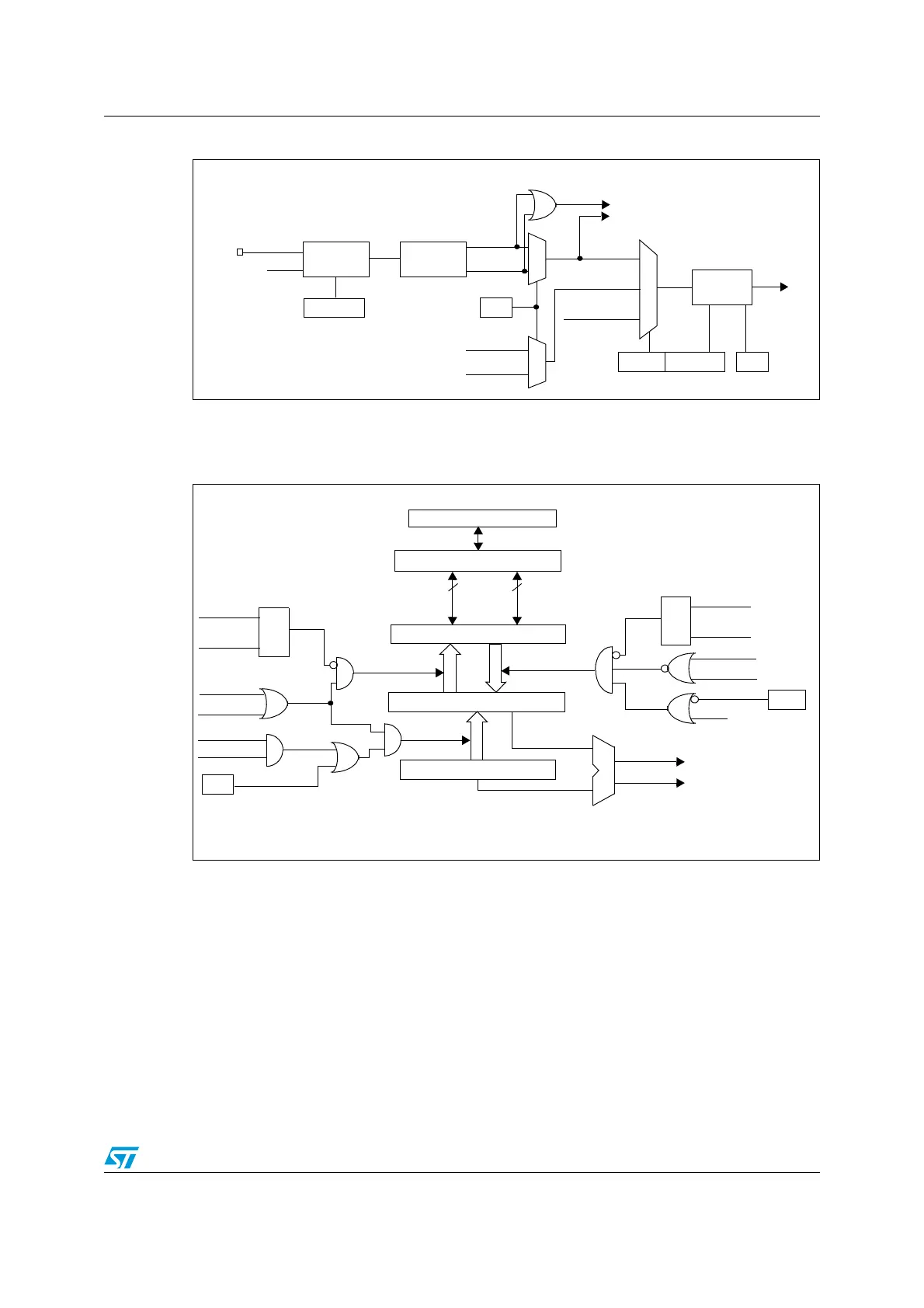

The output stage generates an intermediate waveform which is then used for reference:

OCxRef (active high). The polarity acts at the end of the chain.

Figure 51. Capture/compare channel 1 main circuit

TI1

0

1

TIM1_CCER

CC1P

divider

/1, /2, /4, /8

ICPS[1:0]

TI1F_ED

filter

ICF[3:0]

down-counter

TIM1_CCMR1

Edge

Detector

TI1F_rising

TI1F_falling

to the slave mode controller

TI1FP1

11

01

TIM1_CCMR1

CC1S[1:0]

IC1

TI2FP1

TRC

(from channel 2)

(from slave mode

controller)

10

f

DTS

TIM1_CCER

CC1E

IC1PS

TI1F

0

1

TI2F_rising

TI2F_falling

(from channel 2)

CC1E

Capture/Compare Shadow Register

comparator

Capture/Compare Preload Register

Counter

ic1ps

CC1S[0]

CC1S[1]

capture

input

mode

S

R

read CCR1H

read CCR1L

read_in_progress

capture_transfer

CC1S[0]

CC1S[1]

S

R

write CCR1H

write CCR1L

write_in_progress

output

mode

UEV

OC1PE

(from time

compare_transfer

APB Bus

8

8

high

low

(if 16-bit)

MCU-PERIPHERAL INTERFACE

TIM1_CCMR1

OC1PE

base unit)

CNT>CCR1

CNT=CCR1

TIM1_EGR

CC1G

Loading...

Loading...