UM0306 Backup registers (BKP)

135/519

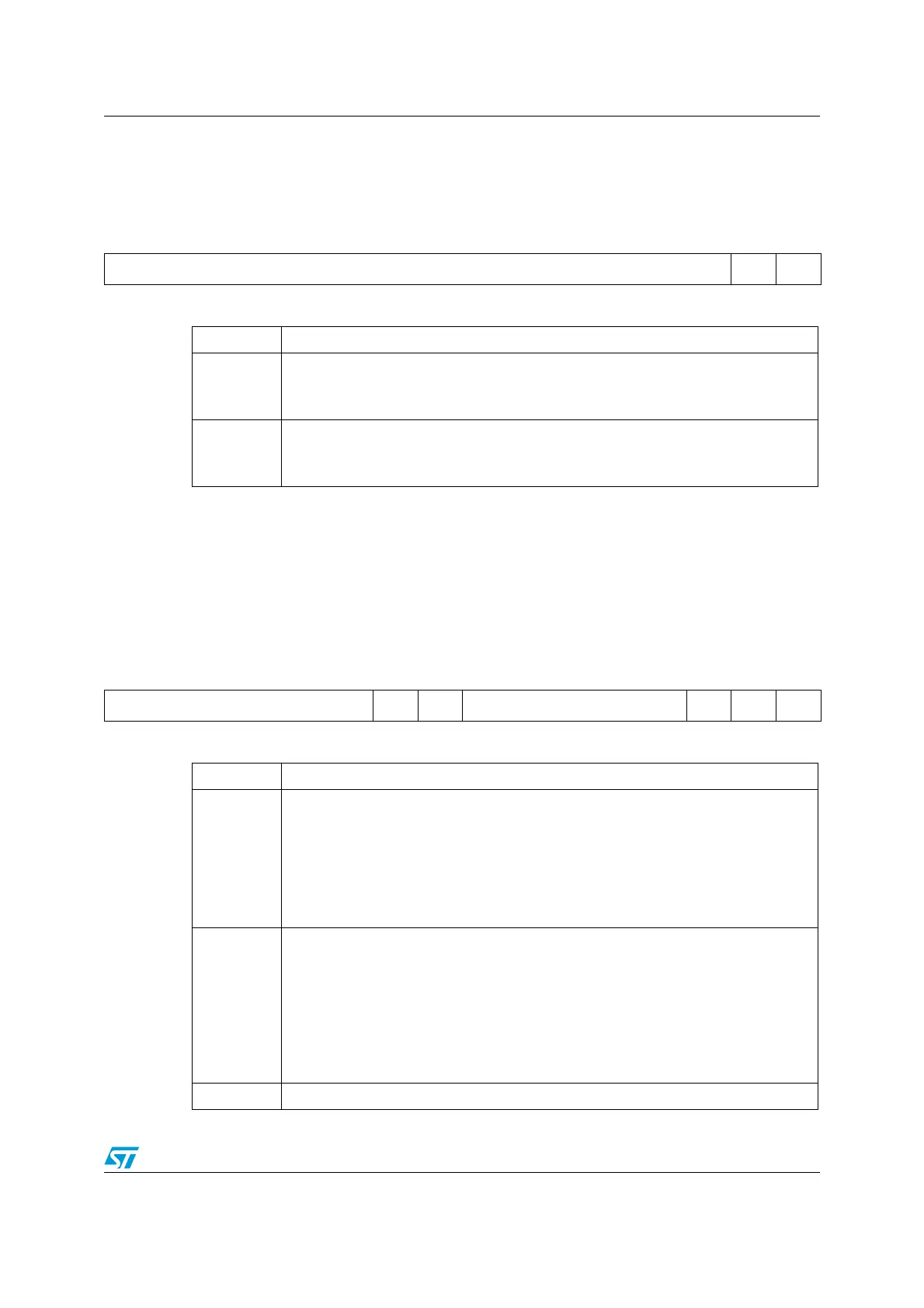

9.5.3 Backup control register (BKP_CR)

Address Offset: 30h

Reset Value: 0000 0000 0000 0000 (0000h)

Note: Setting the TPAL and TPE bits at the same time is always safe, however resetting both at

the same time can generate a spurious Tamper event. For this reason it is recommended to

change the TPAL bit only when the TPE bit is reset.

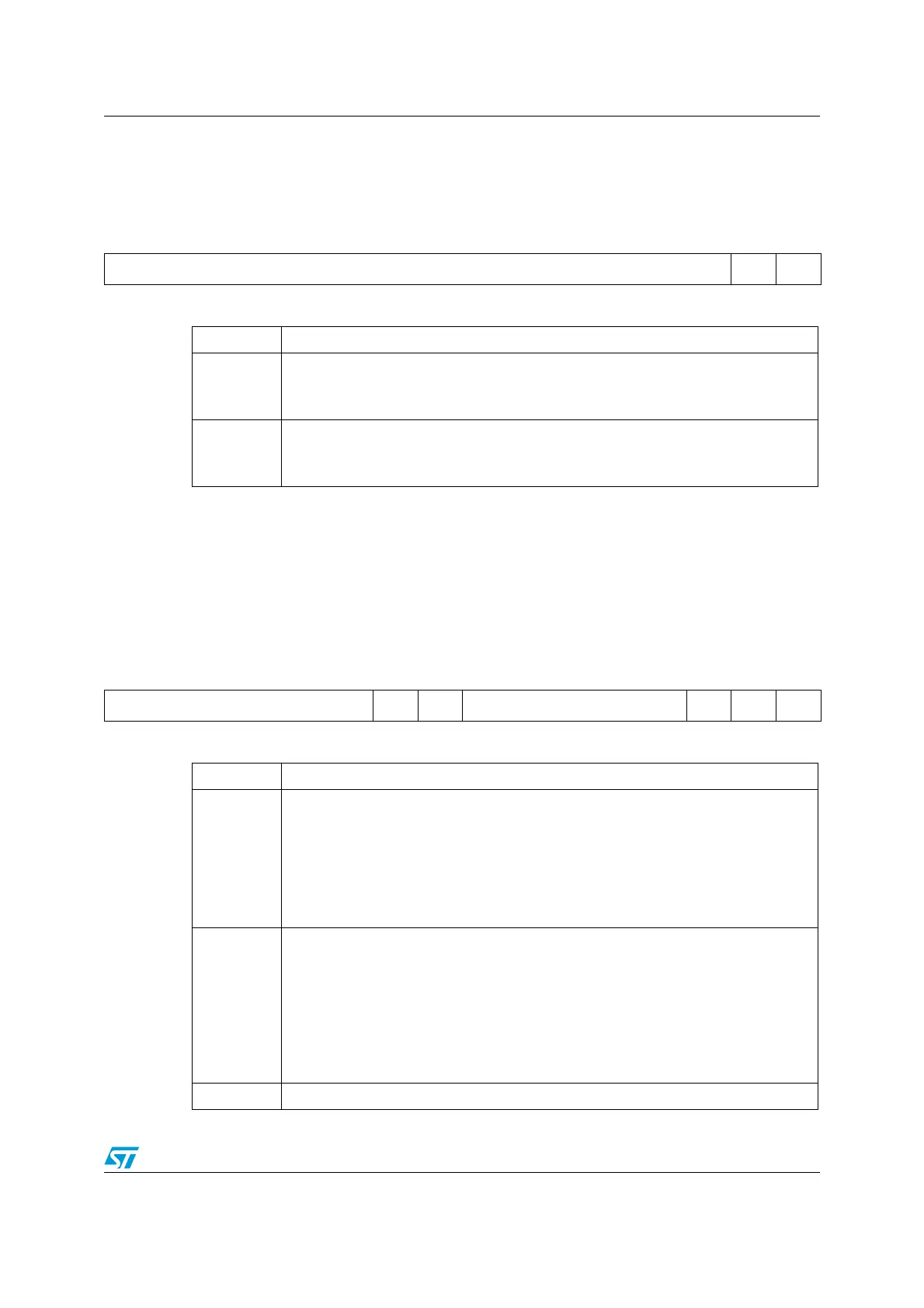

9.5.4 Backup control/status register (BKP_CSR)

Address Offset: 34h

Reset Value: 0000 0000 0000 0000 (0000h)

15

14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

Reserved TPAL TPE

rw rw

Bits 15:2 Reserved, always read as 0.

Bit 1

TPAL Tamper pin active level

0: A high level on the Tamper pin resets all data backup registers (if TPE bit is set).

1: A low level on the Tamper pin resets all data backup registers (if TPE bit is set).

Bit 0

TPE Tamper pin enable

0: The Tamper pin is free for general purpose I/O

1: Tamper alternate I/O function is activated.

15

14 13 12 11 10 9 8 7 6 5 4 3 2 1

0

Reserved TIF TEF Reserved TPIE CTI CTE

rr rwww

Bits 15:10 Reserved, always read as 0.

Bit 9

TIF Tamper Interrupt Flag

This bit is set by hardware when a Tamper event is detected and the TPIE bit is set.

It is cleared by writing 1 to the CTI bit (also clears the interrupt). It is also cleared if

the TPIE bit is reset.

0: No Tamper interrupt

1: A Tamper interrupt occurred

Note: This bit is reset only by a system reset and wake-up from STANDBY mode.

Bit 8

TEF Tamper Event Flag

This bit is set by hardware when a Tamper event is detected. It is cleared by writing

1 to the CTE bit.

0: No Tamper event

1: A Tamper event occurred

Note: A Tamper event resets all the BKP_DRx registers. They are held in reset as

long as the TEF bit is set. If a write to the BKP_DRx registers is performed while this

bit is set, the value will not be stored.

Bits 7:3 Reserved, always read as 0.

Loading...

Loading...