UM0306 DMA controller (DMA)

117/519

7.4.4 DMA channel x number of data register (DMA_CNDTRx) (x = 1 ..7)

Address Offset: 0Ch + 20d x Channel number

Reset Value: 0000 0000 (00h)

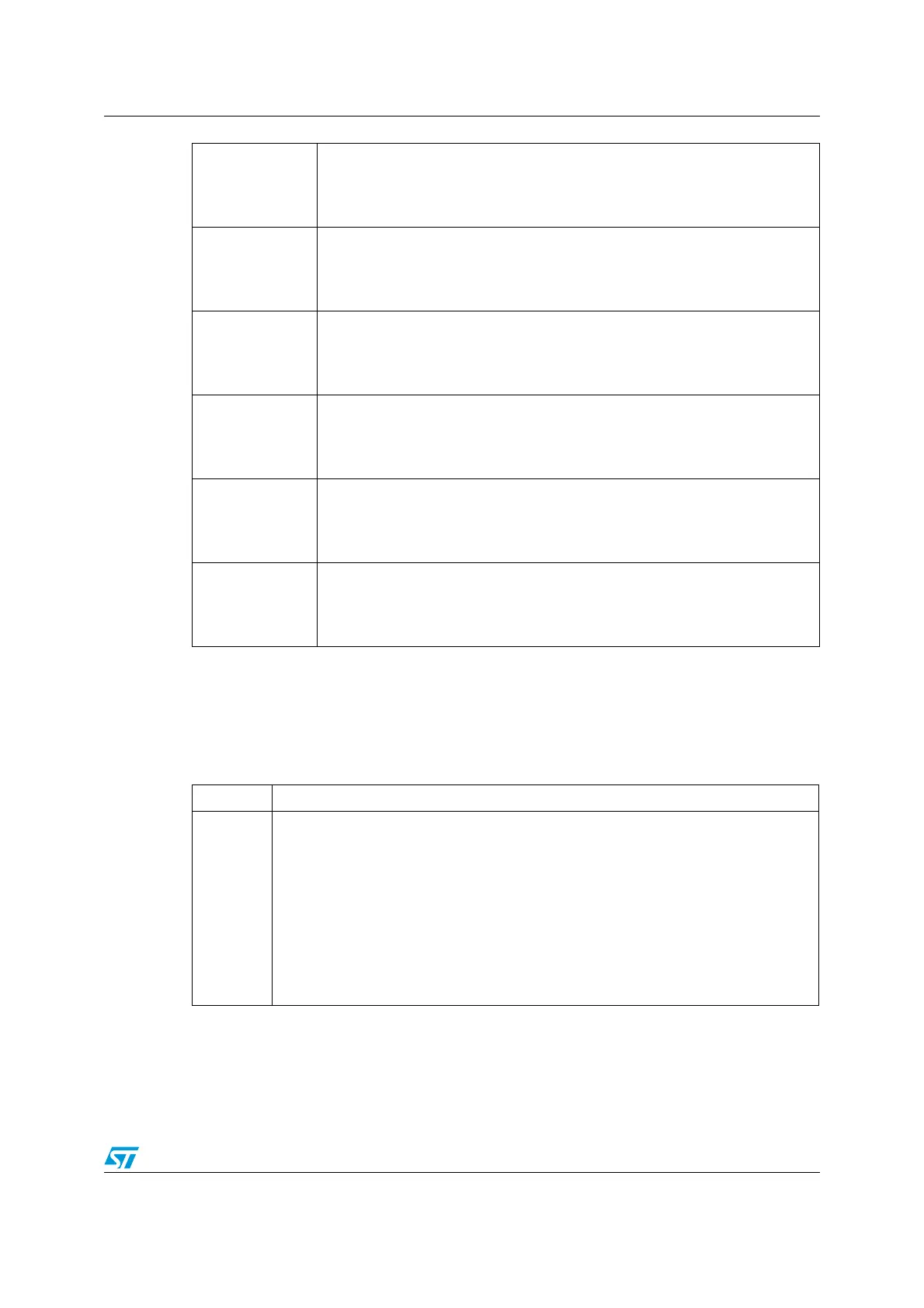

Bit 5

CIRC: Circular mode

This bit is set and cleared by software.

0: Circular mode disabled

1: Circular mode enabled

Bit 4

DIR: Data transfer direction

This bit is set and cleared by software.

0: Read from peripheral

1: Read from memory

Bit 3

TEIE: Transfer error interrupt enable

This bit is set and cleared by software.

0: TE interrupt disabled

1: TE interrupt enabled

Bit 2

HTIE: Half Transfer interrupt enable

This bit is set and cleared by software.

0: HT interrupt disabled

1: HT interrupt enabled

Bit 1

TCIE: Transfer complete interrupt enable

This bit is set and cleared by software.

0: TC interrupt disabled

1: TC interrupt enabled

Bit 0

EN: Channel enable

This bit is set and cleared by software.

0: Channel disabled

1: Channel enabled

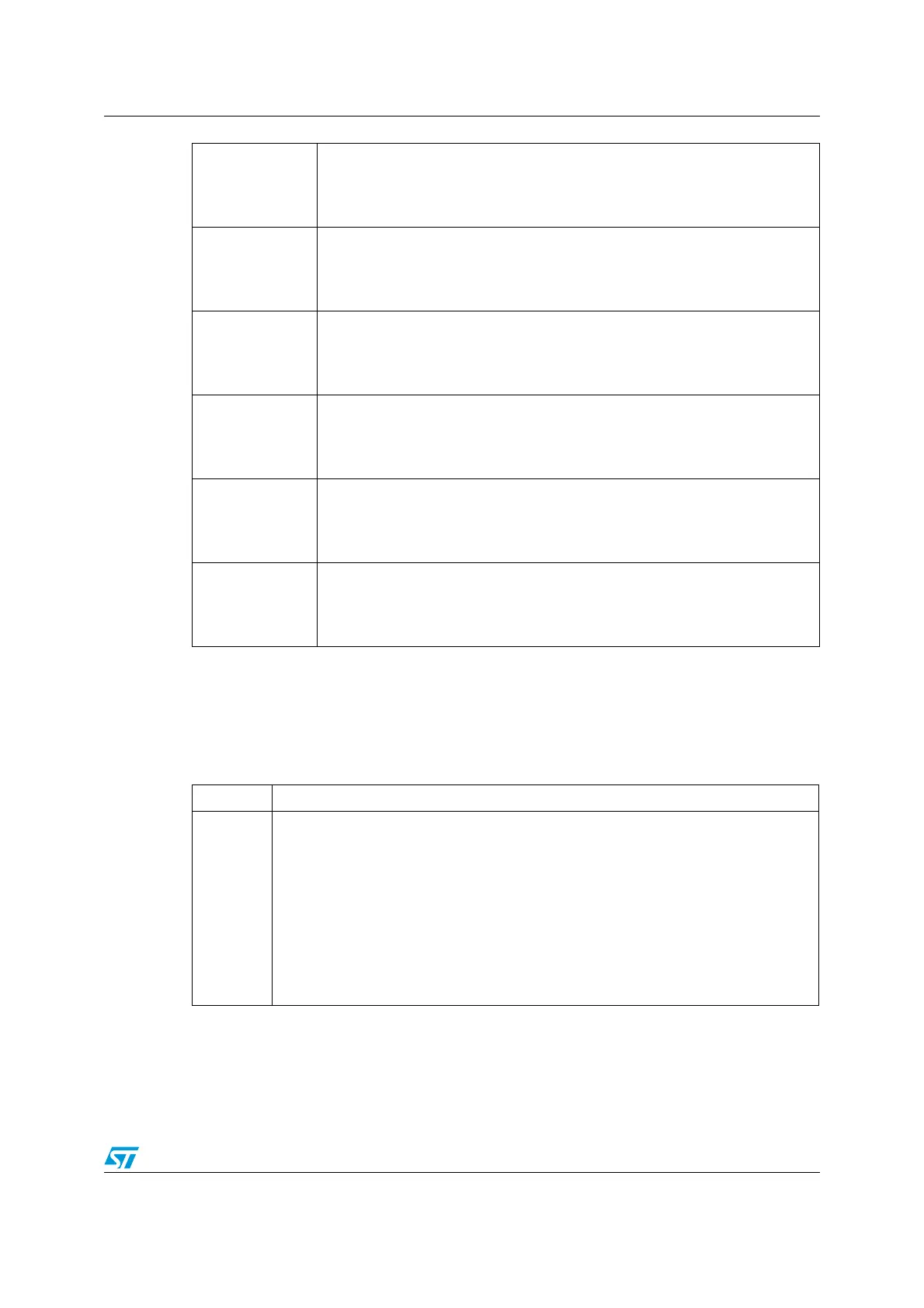

Bits 31:16 Reserved, always read as 0.

Bits 15:0

NDT[15:0]: Number of data to Transfer

Number of data to be transferred (0 up to 65535). This register can only be written

when the channel is disabled. Once the channel is enabled, this register is read-only,

indicating the remaining bytes to be transmitted. This register decrements after each

DMA transfer.

Once the transfer is completed, this register can either stay at zero or be reloaded

automatically by the value previously programmed if the channel is configured in

auto-reload mode.

If this register is zero, no transaction can be served whether the channel is enabled or

not.

Loading...

Loading...