Backup registers (BKP) UM0306

134/519

9.4 RTC calibration

For measurement purposes, the 32.768 kHZ RTC clock can be output on the Tamper pin.

This is enabled by setting the CCO bit in the RTC clock calibration register (BKP_RTCCR).

The clock can be slowed down by up to 121 ppm by configuring CAL[6:0] bits.

9.5 BKP register description

Refer to Section 1.1 on page 23 for a list of abbreviations used in register descriptions.

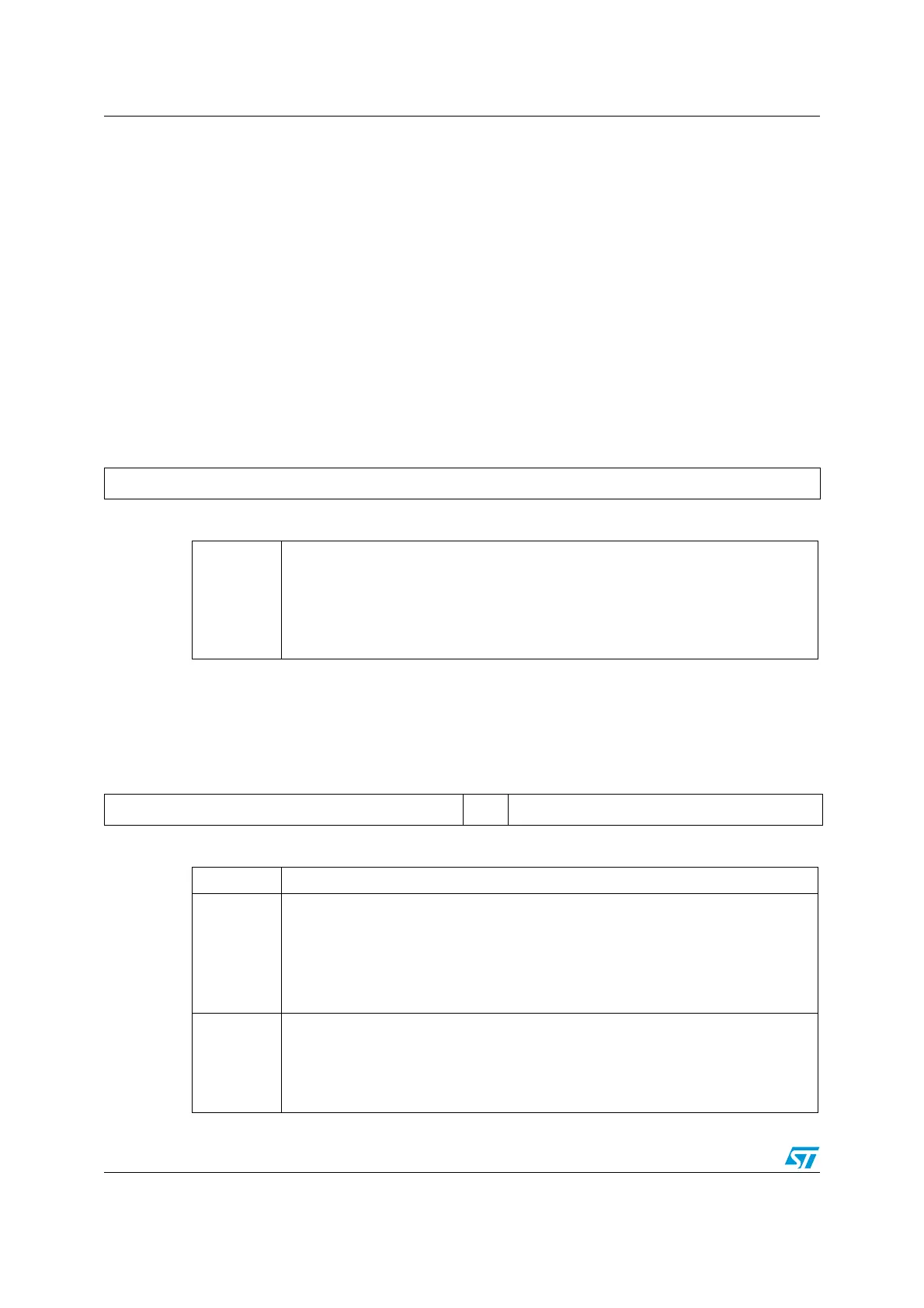

9.5.1 Backup data register x (BKP_DRx) (x = 1 ..10)

Address Offset: 04h to 28h

Reset Value: 0000 0000 0000 0000 (0000h)

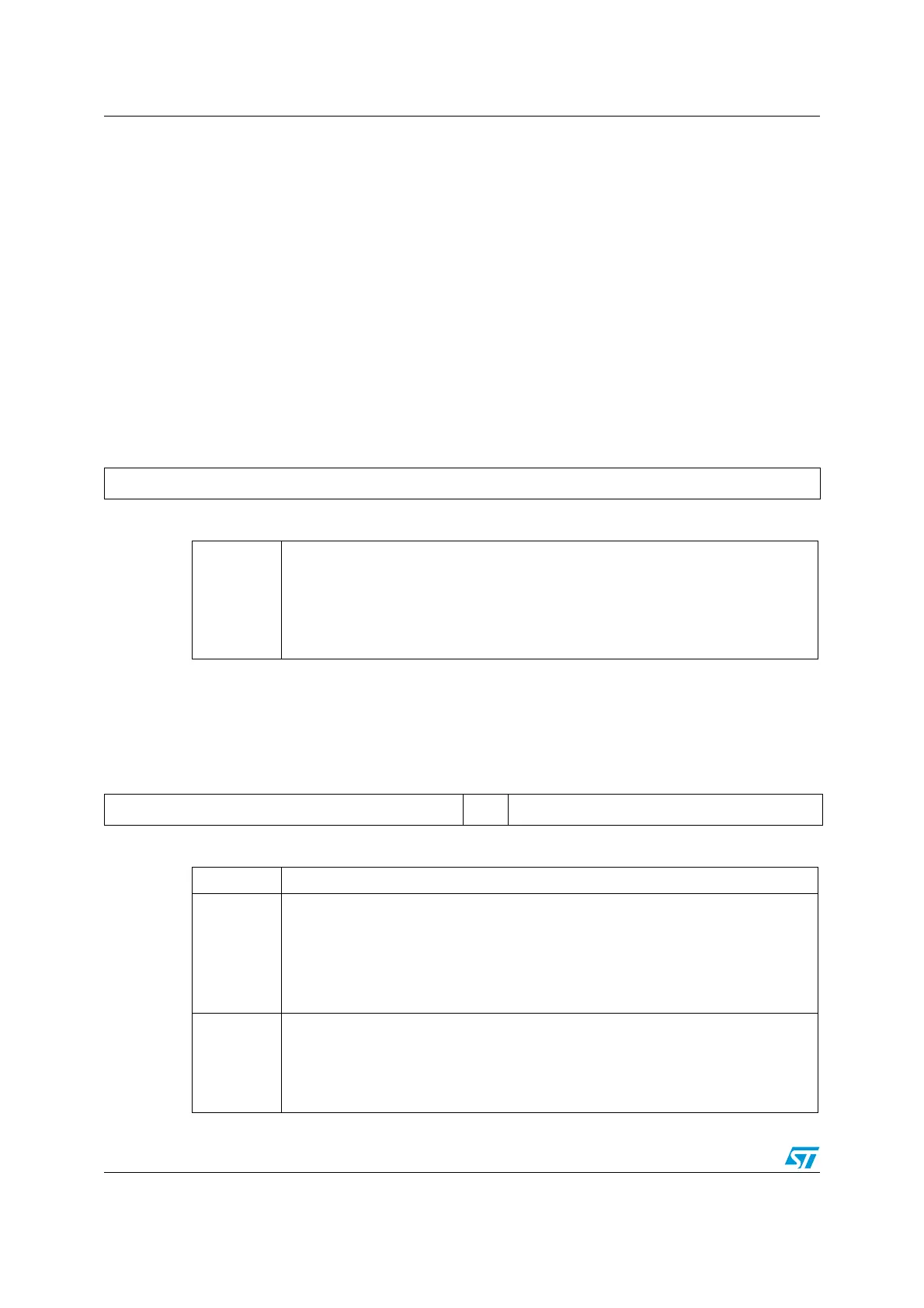

9.5.2 RTC clock calibration register (BKP_RTCCR)

Address Offset: 2Ch

Reset Value: 0000 0000 0000 0000 (0000h)

15

1413121110987654321

0

D[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0

D[15:0] Backup data.

These bits can be written with user data.

Note: The BKP_DRx registers are not reset by a System reset or Power reset or when

the device wakes up from STANDBY mode.

They are reset by a Backup Domain reset or by a Tamper pin event (if the Tamper pin

function is activated).

15

1413121110987654321

0

Reserved CCO CAL[6:0]

rw rw rw rw rw rw rw rw

Bits 15:8 Reserved, always read as 0.

Bit 7

CCO Calibration Clock Output

0: No effect

1: Setting this bit outputs the RTC clock with frequency divided by 64 on the Tamper

pin. The Tamper pin must not be enabled while the CCO bit is set in order to avoid

unwanted Tamper detection.

Note: This bit is reset when the VDD supply is powered off.

Bit 6:0

CAL[6:0] Calibration value

This value indicates the number of clock pulses that will be ignored every 2^20 clock

pulses. This allows the calibration of the RTC, slowing down the clock by steps of

1000000/2^20 PPM.

The clock of the RTC can be slowed down from 0 to 121PPM.

Loading...

Loading...