UM0306 Reset and clock control (RCC)

67/519

4.3.8 APB1 Peripheral Clock enable register (RCC_APB1ENR)

Address: 1Ch

Reset value: 0000 0000h

Access: word, half-word and byte access

No wait state, except if the access occurs while an access to a peripheral on APB1 domain

is on going. In this case, wait states are inserted until this access to APB1 peripheral is

finished.

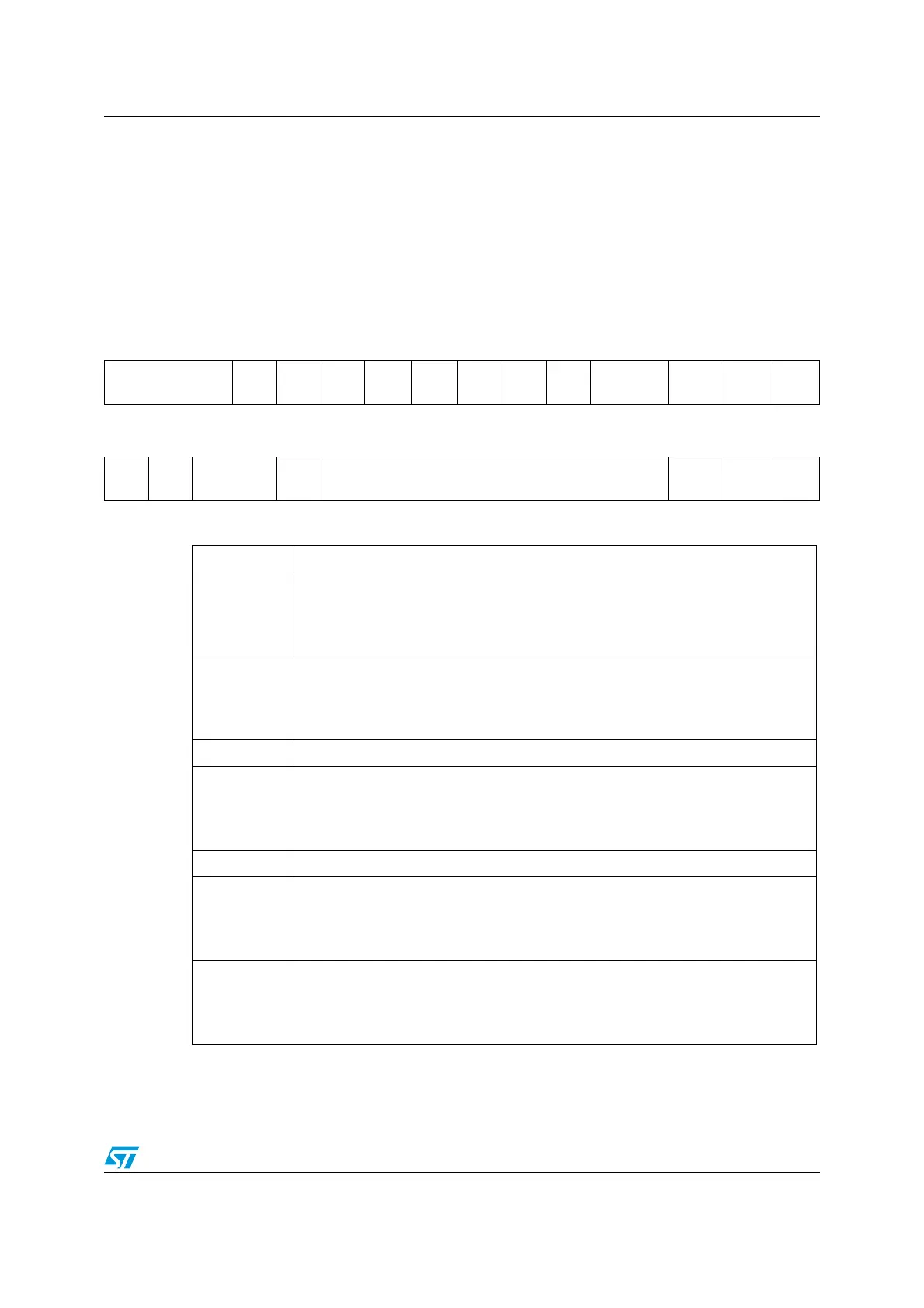

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

PWR

EN

BKP

EN

Res.

CAN

EN

Res.

USB

EN

I2C2

EN

I2C1

EN

Reserved

USART3

EN

USART2

EN

Res.

rw rw rw rw rw rw rw rw

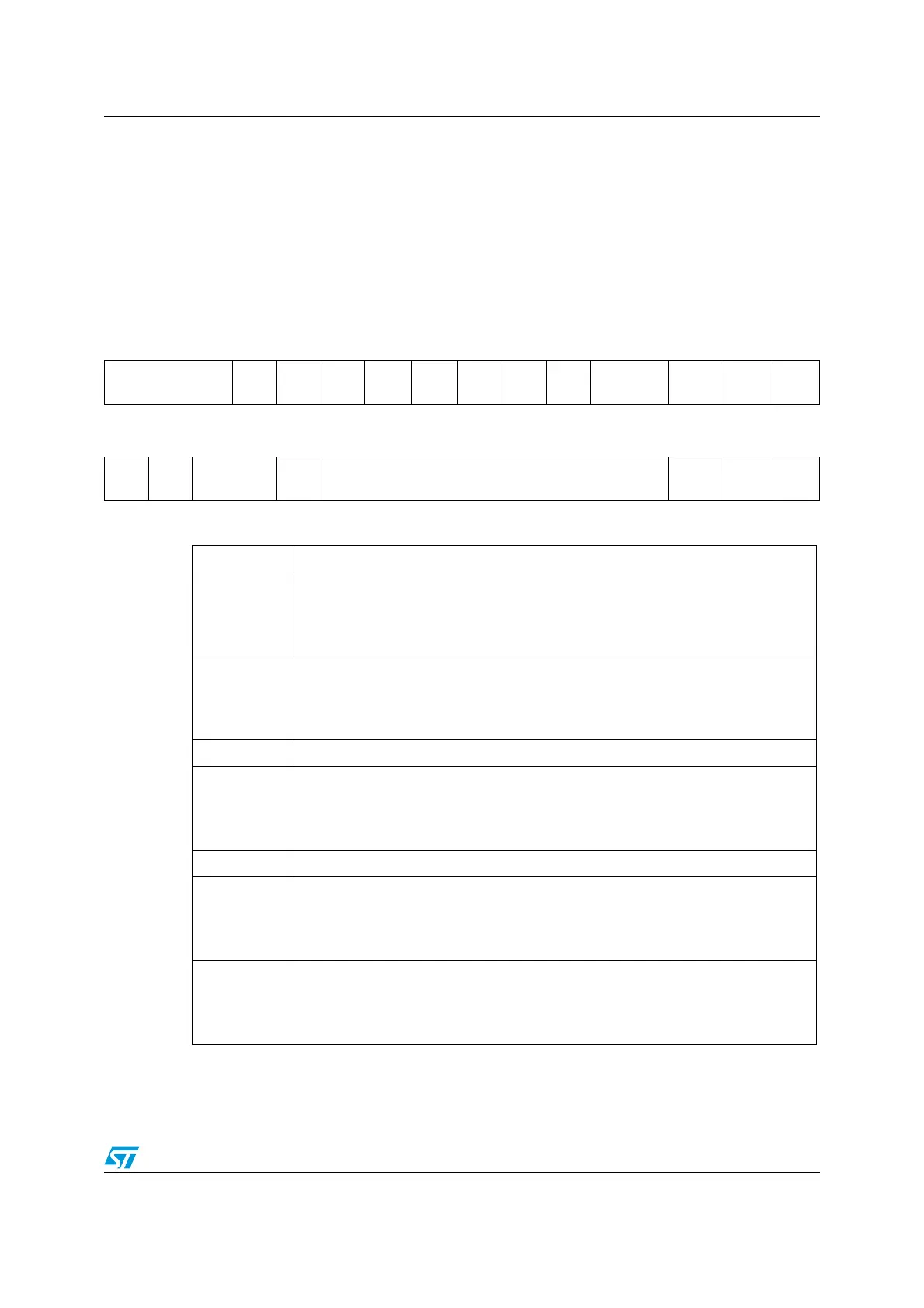

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res.

SPI2

EN

Reserved

WWD

GEN

Reserved

TIM4

EN

TIM3

EN

TIM2

EN

rw rw rw rw rw

Bits 31:29 Reserved, always read as 0.

Bit 28

PWREN Power interface clock enable

Set and reset by software.

0: Power interface clock disabled

1: Power interface clock enable

Bit 27

BKPEN Backup interface clock enable

Set and reset by software.

0: Backup interface clock disabled

1: Backup interface clock enabled

Bit 26 Reserved, always read as 0.

Bit 25

CANEN CAN clock enable

Set and reset by software.

0: CAN clock disabled

1: CAN clock enabled

Bit 24 Reserved, always read as 0.

Bit 23

USBEN USB clock enable

Set and reset by software.

0: USB clock disabled

1: USB clock enabled

Bit 22

I2C2EN I2C 2 clock enable

Set and reset by software.

0: I2C 2 clock disabled

1: I2C 2 clock enabled

Loading...

Loading...