General purpose timer (TIMx) UM0306

236/519

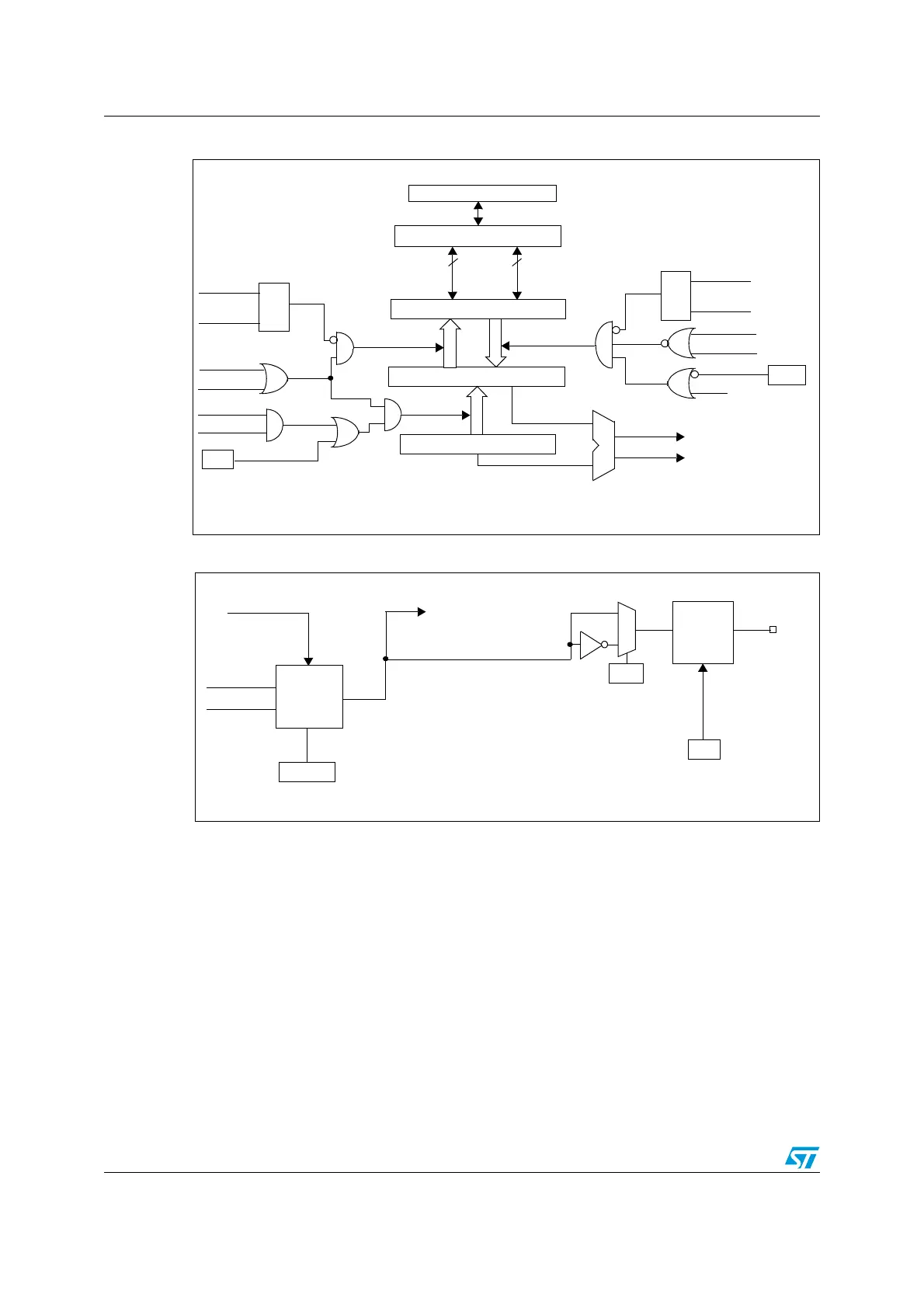

Figure 98. Capture/compare channel 1 main circuit

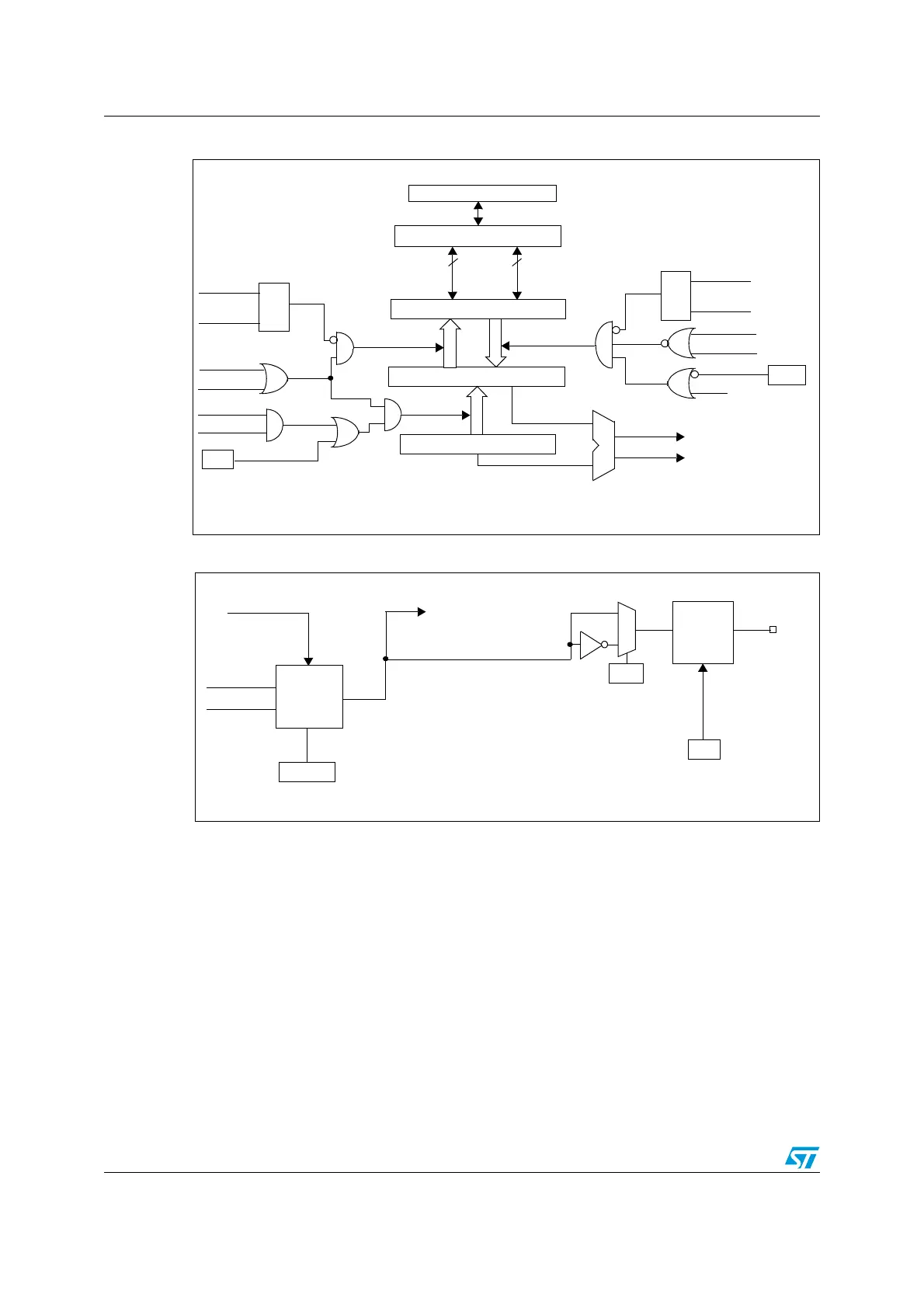

Figure 99. Output stage of capture/compare channel (channel 1)

The capture/compare block is made of one preload register and one shadow register. Write

and read always access the preload register.

In capture mode, captures are actually done in the shadow register, which is copied into the

preload register.

In compare mode, the content of the preload register is copied into the shadow register

which is compared to the counter.

13.4.5 Input capture mode

In Input capture mode, the Capture/Compare Registers (TIMx_CCRx) are used to latch the

value of the counter after a transition detected by the corresponding ICx signal. When a

capture occurs, the corresponding CCXIF flag (TIMx_SR register) is set and an interrupt or

a DMA request can be sent if they are enabled. If a capture occurs while the CCxIF flag was

already high, then the over-capture flag CCxOF (TIMx_SR register) is set. CCxIF can be

CC1E

Capture/Compare Shadow Register

comparator

Capture/Compare Preload Register

Counter

ic1ps

CC1S[0]

CC1S[1]

capture

input

mode

S

R

read CCR1H

read CCR1L

read_in_progress

capture_transfer

CC1S[0]

CC1S[1]

S

R

write CCR1H

write CCR1L

write_in_progress

output

mode

UEV

OC1PE

(from time

compare_transfer

APB Bus

8

8

high

low

(if 16-bit)

MCU-PERIPHERAL INTERFACE

TIMx_CCMR1

OC1PE

base unit)

CNT>CCR1

CNT=CCR1

TIMx_EGR

CC1G

Output Mode

CNT > CCR1

CNT = CCR1

Controller

TIMx_CCMR1

OC1M[2:0]

oc1ref

0

1

CC1P

TIMx_CCER

Output

Enable

Circuit

OC1

CC1E

TIMx_CCER

To the master mode

controller

ETRF

Loading...

Loading...