UM0306 Window watchdog (WWDG)

147/519

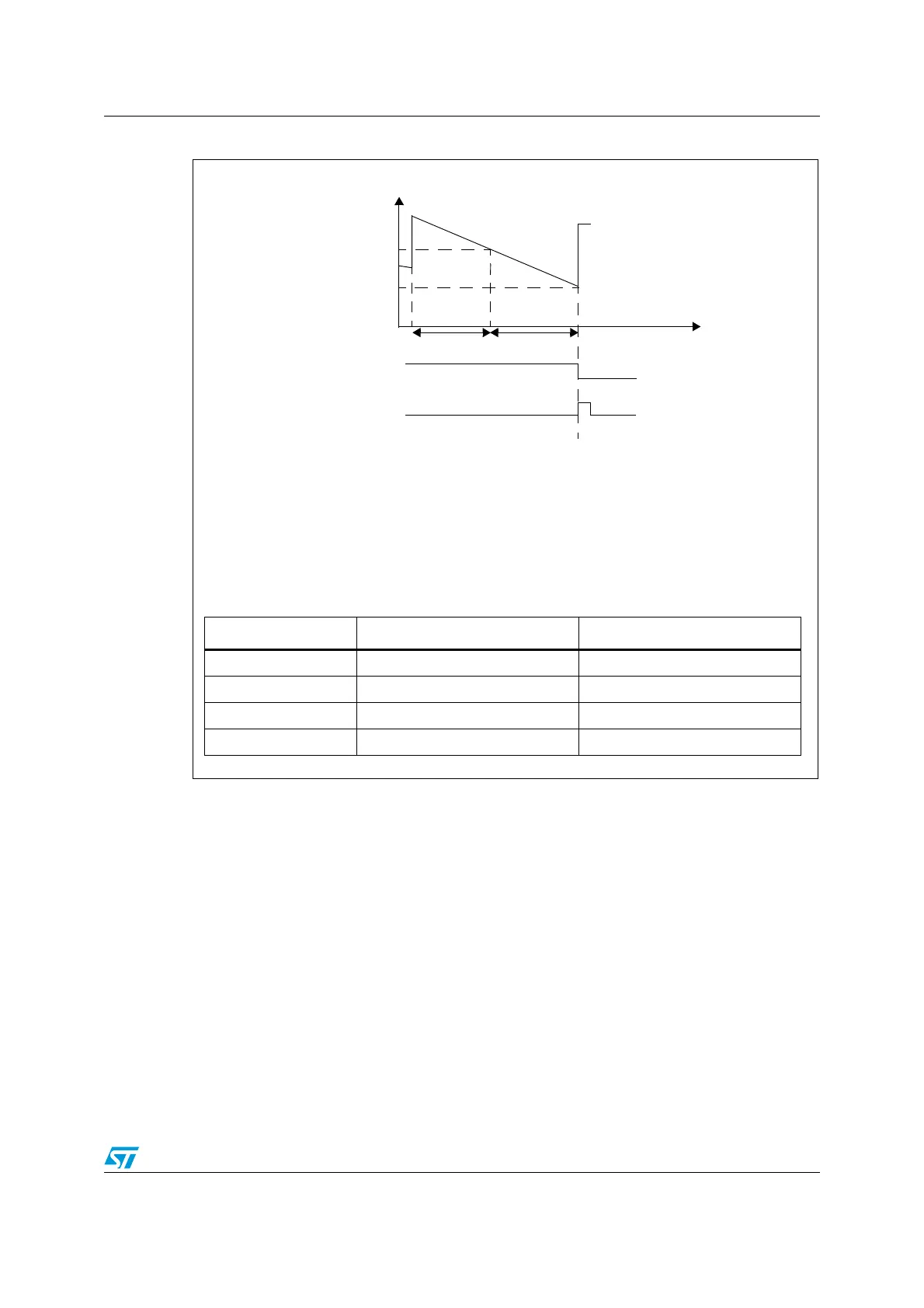

Figure 23. Window watchdog timing diagram

11.5 Debug mode

When the microcontroller enters debug mode (Cortex-M3 core halted), the WWDG counter

either continues to work normally or stops, depending on DBG_WWDG_STOP configuration

bit in DBG module. For more details, refer to Section 20.15.2: Debug support for timers and

watchdog and bxCAN.

T6 bit

Reset

W[6:0]

T[6:0] CNT downcounter

time

Refresh WindowRefresh not allowed

3Fh

The formula to calculate the timeout value is given by:

where:

T

WWDG

: WWDG timeout

T

PCLK1

: APB1 Clock period measured in ms

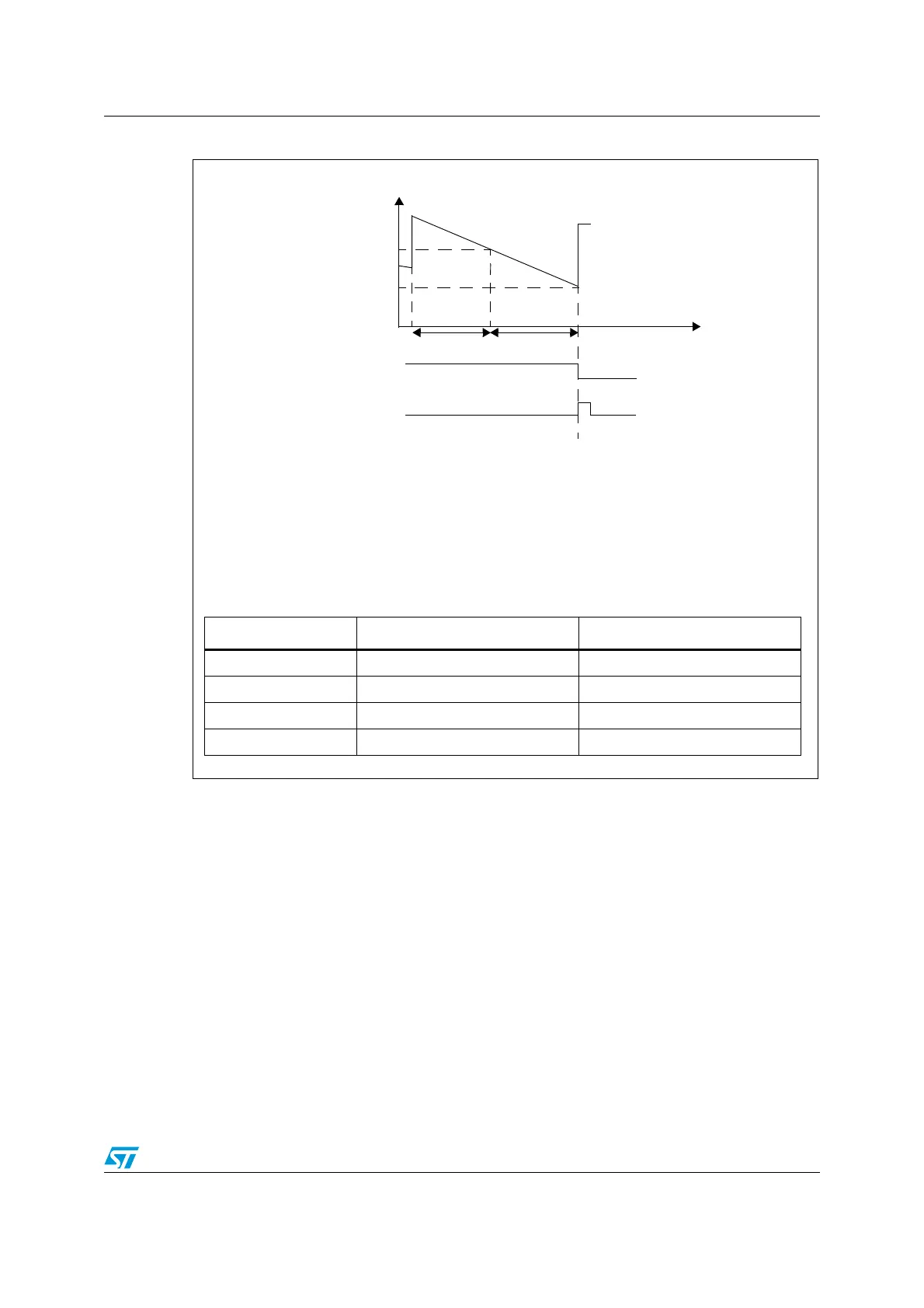

Min-max timeout value @36MHz (PCLK1)

WDGTB Min Timeout Value Max Timout Value

0 113 µs 7.28 ms

1 227 µs 14.56 ms

2 455 µs 29.12 ms

3 910 µs 58.25 ms

T

WWDG

T

PCLK1

4096× 2

WDGTB

× T5:0[]1+()×= ms();

Loading...

Loading...