UM0306 General purpose timer (TIMx)

255/519

As in the previous example, you can initialize both counters before starting counting.

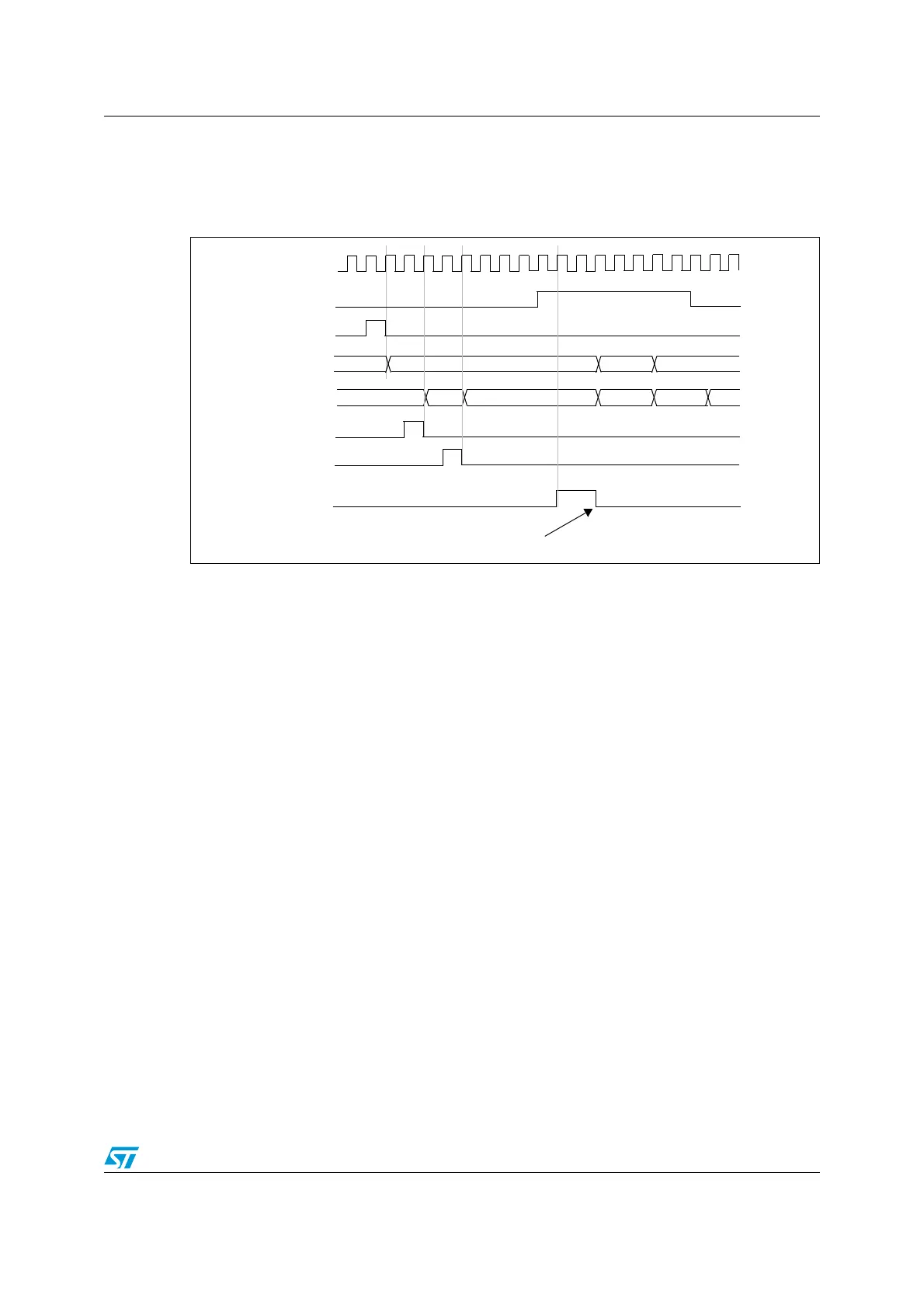

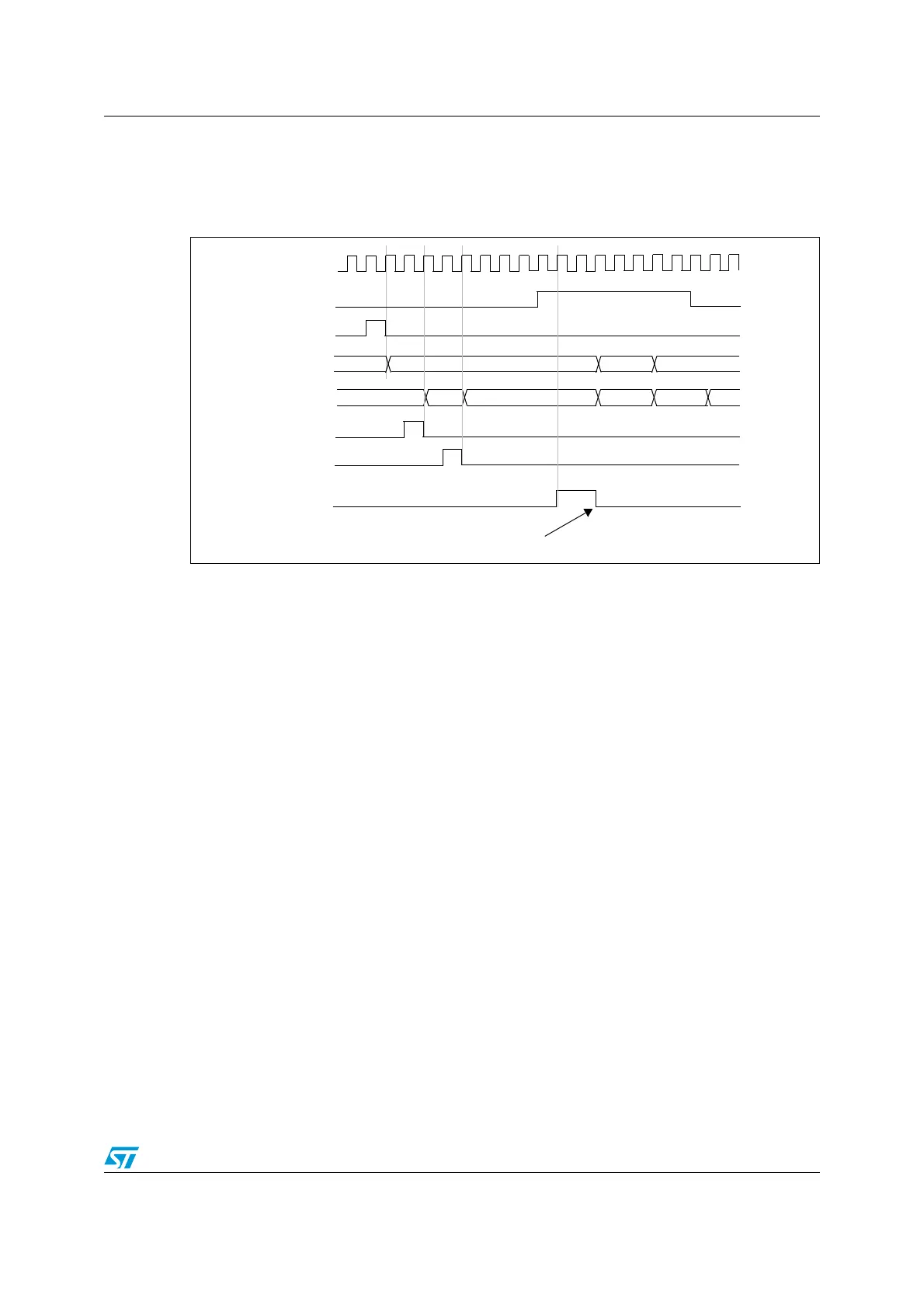

Figure 116 shows the behavior with the same configuration as in Figure 115 but in trigger

mode instead of gated mode (SMS=110 in the TIM2_SMCR register).

Figure 116. Triggering Timer 2 with ENABLE of Timer 1

Using one timer as prescaler for another timer

For example, you can configure Timer 1 to act as a prescaler for Timer 2. Refer to

Figure 112 for connections. To do this:

● Configure Timer 1 master mode to send its Update Event (UEV) as trigger output

(MMS=010 in the TIM1_CR2 register). then it outputs a periodic signal on each counter

overflow.

● Configure the Timer 1 period (TIM1_ARR registers).

● Configure Timer 2 to get the input trigger from Timer 1 (TS=001 in the TIM2_SMCR

register).

● Configure Timer 2 in external clock mode 1 (SMS=111 in TIM2_SMCR register).

● Start Timer 2 by writing ‘1’ in the CEN bit (TIM2_CR1 register).

● Start Timer 1 by writing ‘1’ in the CEN bit (TIM1_CR1 register).

Starting 2 timers synchronously in response to an external trigger

In this example, we set the enable of timer 1 when its TI1 input rises, and the enable of

Timer 2 with the enable of Timer 1. Refer to Figure 112 for connections. To ensure the

TIMER 2-TIF

Write TIF=0

75 00 01

CK_INT

TIMER1-CEN=cnt_en

TIMER1-CNT

TIMER2-CNT

02

TIMER1-cnt_init

CD 00 E7 E8 EA

TIMER2-cnt_init

TIMER2

write CNT

E9

Loading...

Loading...