Advanced control timer (TIM1) UM0306

198/519

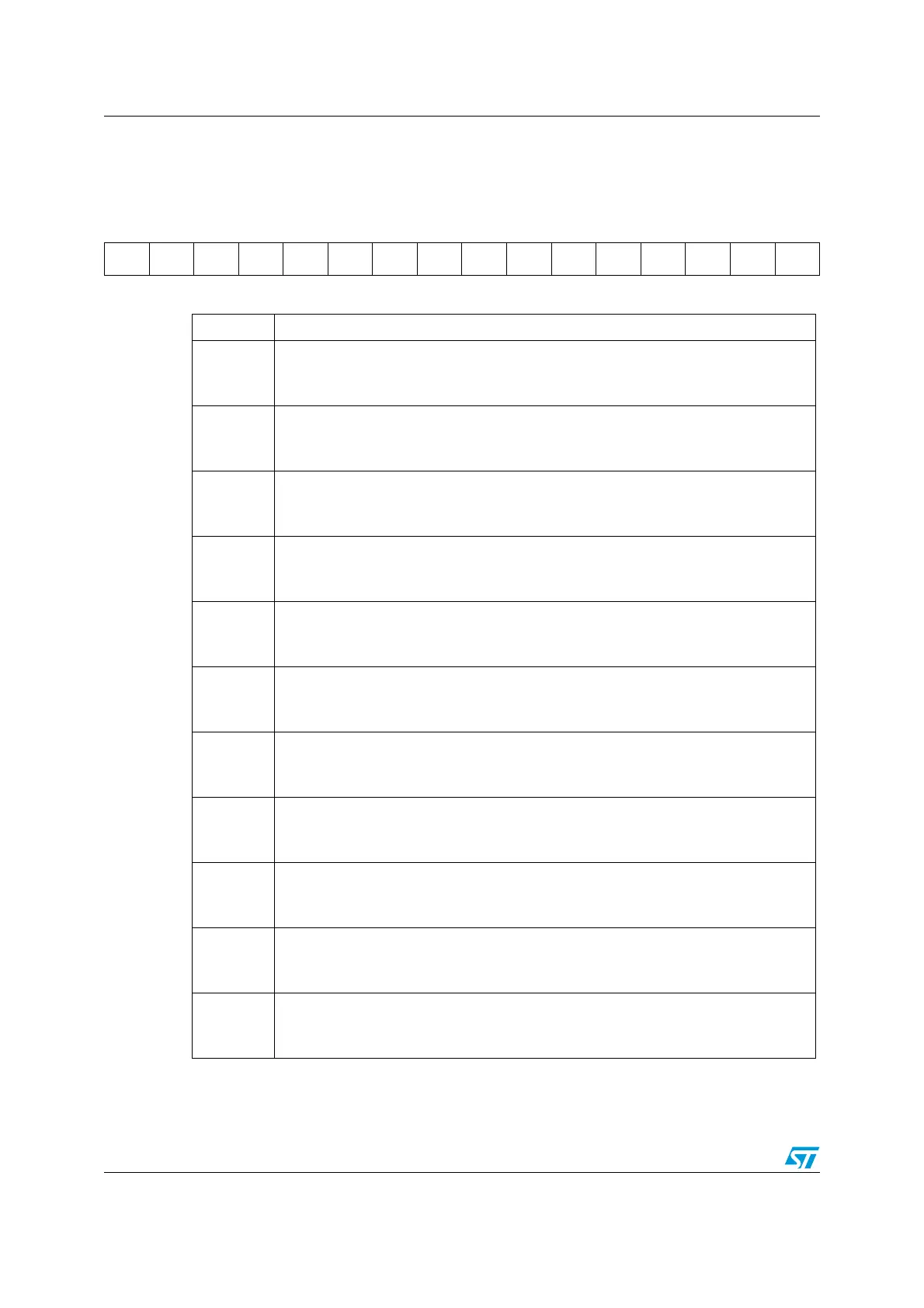

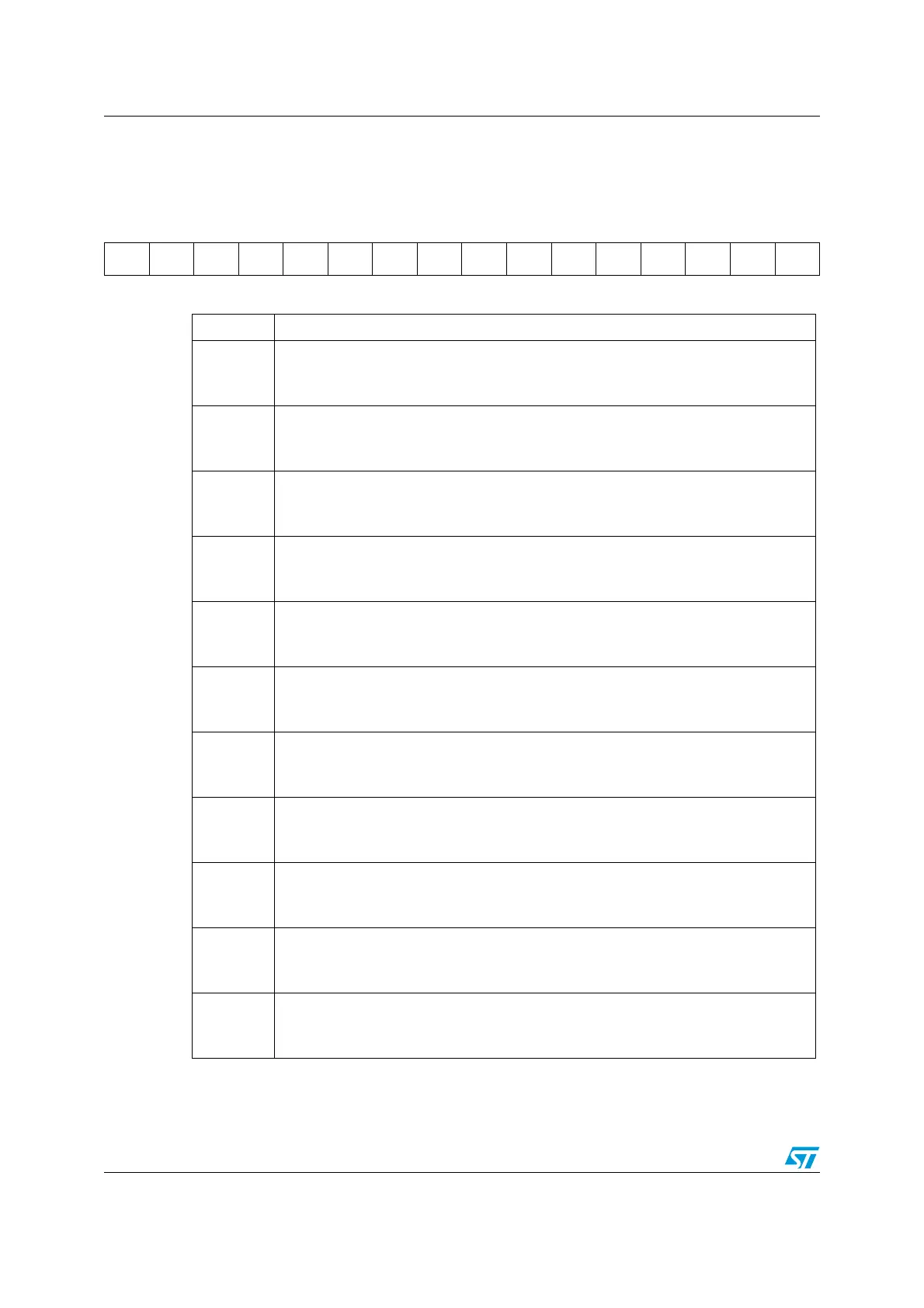

12.5.4 DMA/Interrupt enable register (TIM1_DIER)

Address offset: 0Ch

Reset value: 0000h

1514131211109876543210

Res. TDE

COMD

E

CC4D

E

CC3D

E

CC2D

E

CC1D

E

UDE BIE TIE

COMI

E

CC4IE CC3IE CC2IE CC1IE UIE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 15 Reserved, always read as 0.

Bit 14

TDE: Trigger DMA request enable.

0: Trigger DMA request disabled.

1: Trigger DMA request enabled.

Bit 13

COMDE: COM DMA request enable.

0: COM DMA request disabled.

1: COM DMA request enabled.

Bit 12

CC4DE: Capture/Compare 4 DMA request enable.

0: CC4 DMA request disabled.

1: CC4 DMA request enabled.

Bit 11

CC3DE: Capture/Compare 3 DMA request enable.

0: CC3 DMA request disabled.

1: CC3 DMA request enabled.

Bit 10

CC2DE: Capture/Compare 2 DMA request enable.

0: CC2 DMA request disabled.

1: CC2 DMA request enabled.

Bit 9

CC1DE: Capture/Compare 1 DMA request enable.

0: CC1 DMA request disabled.

1: CC1 DMA request enabled.

Bit 8

UDE: Update DMA request enable.

0: Update DMA request disabled.

1: Update DMA request enabled.

Bit 7

BIE: Break interrupt enable.

0: Break interrupt disabled.

1: Break interrupt enabled.

Bit 6

TIE: Trigger interrupt enable.

0: Trigger interrupt disabled.

1: Trigger interrupt enabled.

Bit 5

COMIE: COM interrupt enable.

0: COM interrupt disabled.

1: COM interrupt enabled.

Bit 4

CC4IE: Capture/Compare 4 interrupt enable.

0: CC4 interrupt disabled.

1: CC4 interrupt enabled.

Loading...

Loading...