UM0306 Memory and bus architecture

27/519

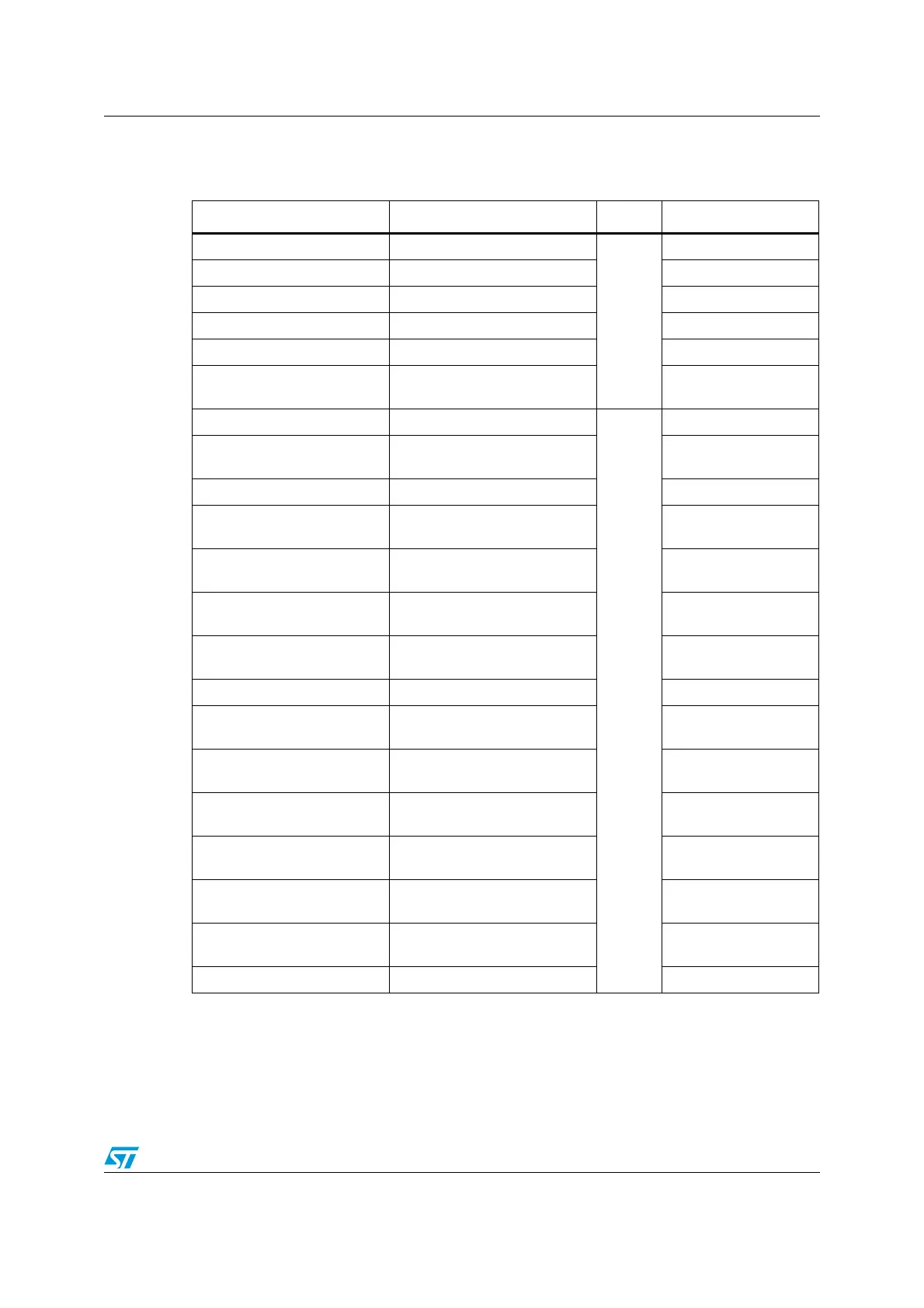

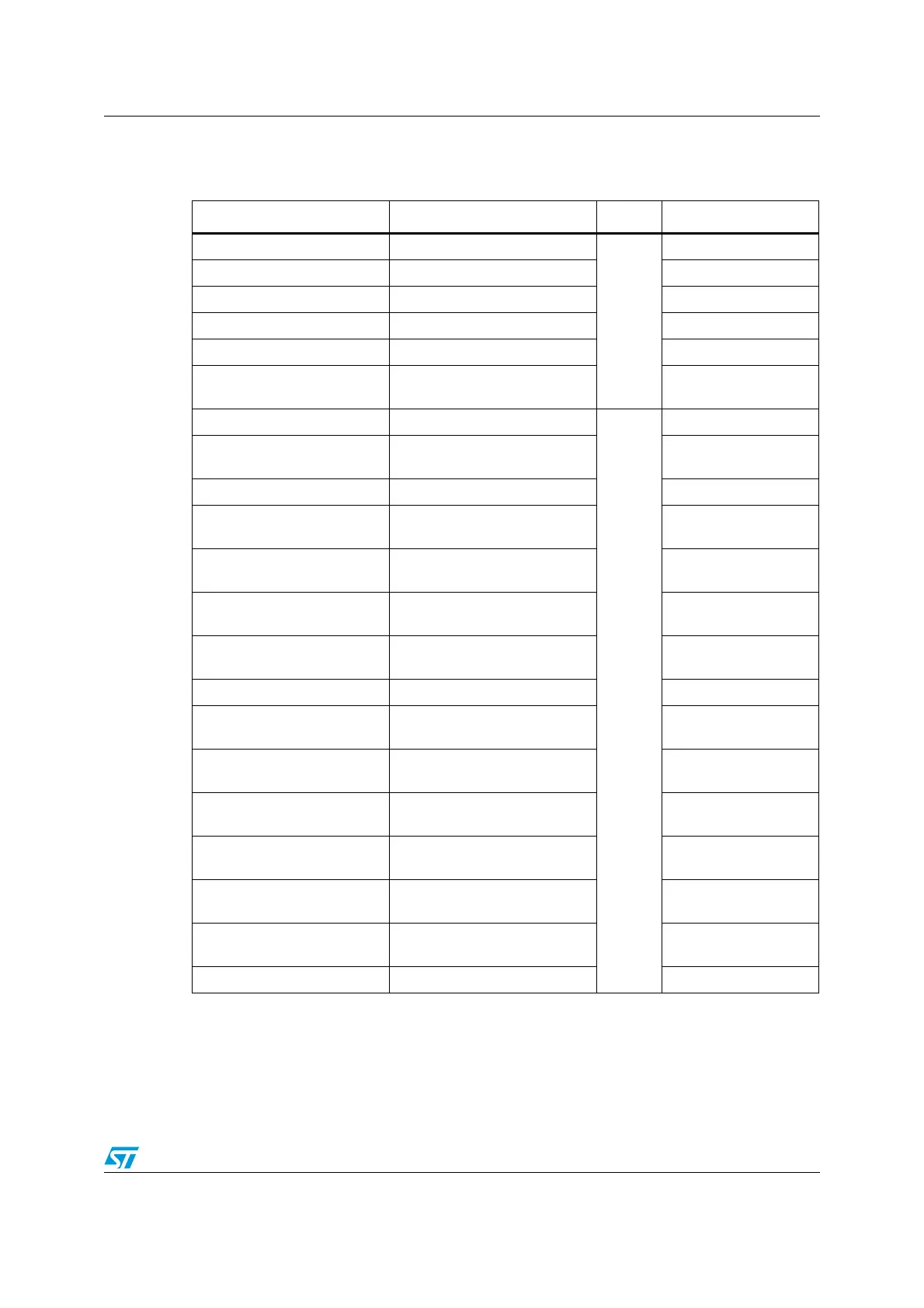

2.3.1 Peripheral memory map

Table 1. Register boundary addresses

Boundary Address Peripheral Bus Register Map

0x4002 2400 - 0x4002 3FFF Reserved

AHB

0x4002 2000 - 0x4002 23FF Flash memory interface

0x4002 1400 - 0x4002 1FFF Reserved

0x4002 1000 - 0x4002 13FF Reset and Clock control RCC Section 4.4 on page 72

0x4002 0400 - 0x4002 0FFF Reserved

0x4002 0000 - 0x4002 03FF DMA

Section 7.5 on page

118

0x4001 3C00 - 0x4001 3FFF Reserved

APB2

0x4001 3800 - 0x4001 3BFF USART1

Section 17.5 on page

418

0x4001 3400 - 0x4001 37FF Reserved

0x4001 3000 - 0x4001 33FF SPI 1

Section 16.5 on page

376

0x4001 2C00 - 0x4001 2FFF TIM1 timer

Section 12.6 on page

219

0x4001 2800 - 0x4001 2BFF ADC2

Section 19.14 on page

485

0x4001 2400 - 0x4001 27FF ADC1

Section 19.14 on page

485

0x4001 2000 - 0x4001 1FFF Reserved

0x4001 1800 - 0x4001 1BFF GPIO Port E

Section 5.5.1 on page

97

0x4001 1400 - 0x4001 17FF GPIO Port D

Section 5.5.1 on page

97

0x4001 1000 - 0x4001 13FF GPIO Port C

Section 5.5.1 on page

97

0X4001 0C00 - 0x4001 0FFF GPIO Port B

Section 5.5.1 on page

97

0x4001 0800 - 0x4001 0BFF GPIO Port A

Section 5.5.1 on page

97

0x4001 0400 - 0x4001 07FF EXTI

Section 6.2 on page

101

0x4001 0000 - 0x4001 03FF AFIO Section 5.5 on page 97

Loading...

Loading...