UM0306 Reset and clock control (RCC)

59/519

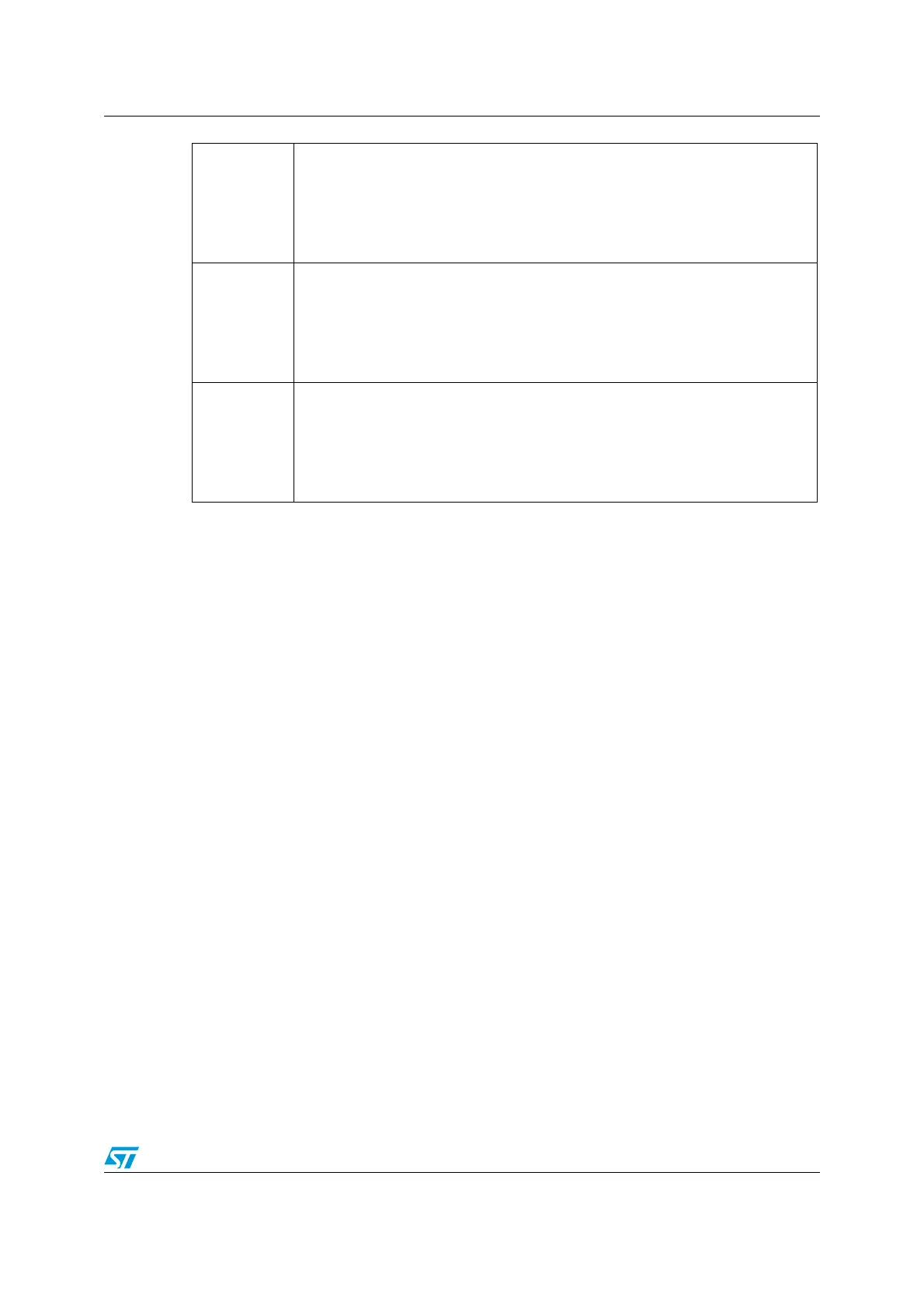

Bit 2

HSIRDYF HSI Ready Interrupt flag

Reset by software by writing HSIRDYC.

Set by hardware when the Internal High Speed clock becomes stable and

HSIRDYDIE is set.

0: No clock ready interrupt caused by the internal 8 MHz RC oscillator

1: Clock ready interrupt caused by the internal 8 MHz RC oscillator

Bit 1

LSERDYF LSE Ready Interrupt flag

Reset by software by writing LSERDYC.

Set by hardware when the External Low Speed clock becomes stable and

LSERDYDIE is set.

0: No clock ready interrupt caused by the external 32 kHz oscillator

1: Clock ready interrupt caused by the external 32 kHz oscillator

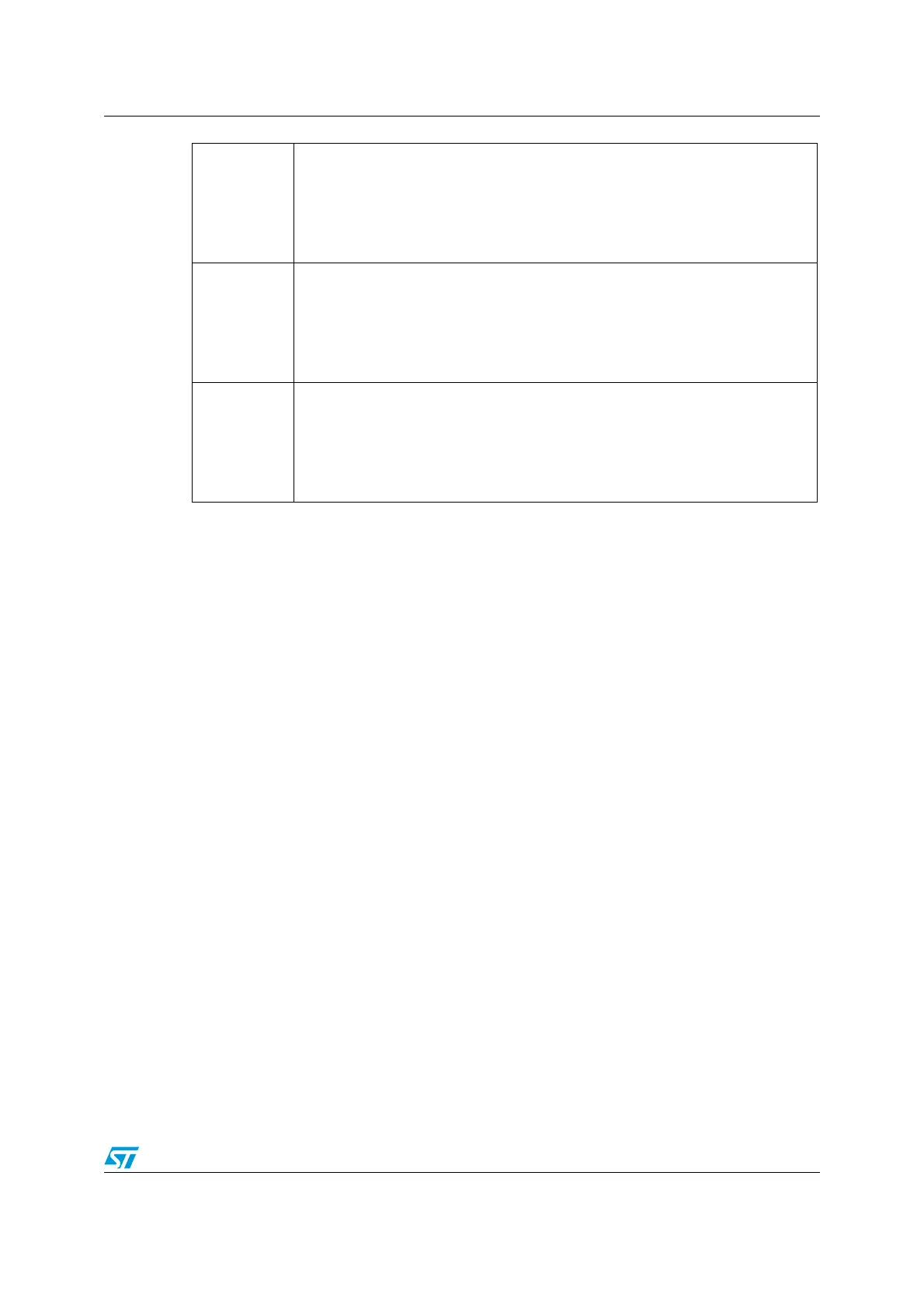

Bit 0

LSIRDYF LSI Ready Interrupt flag

Reset by software by writing LSIRDYC.

Set by hardware when Internal Low Speed clock becomes stable and LSIRDYDIE

is set.

0: No clock ready interrupt caused by the internal RC 32 kHz oscillator

1: Clock ready interrupt caused by the internal RC 32 kHz oscillator

Loading...

Loading...