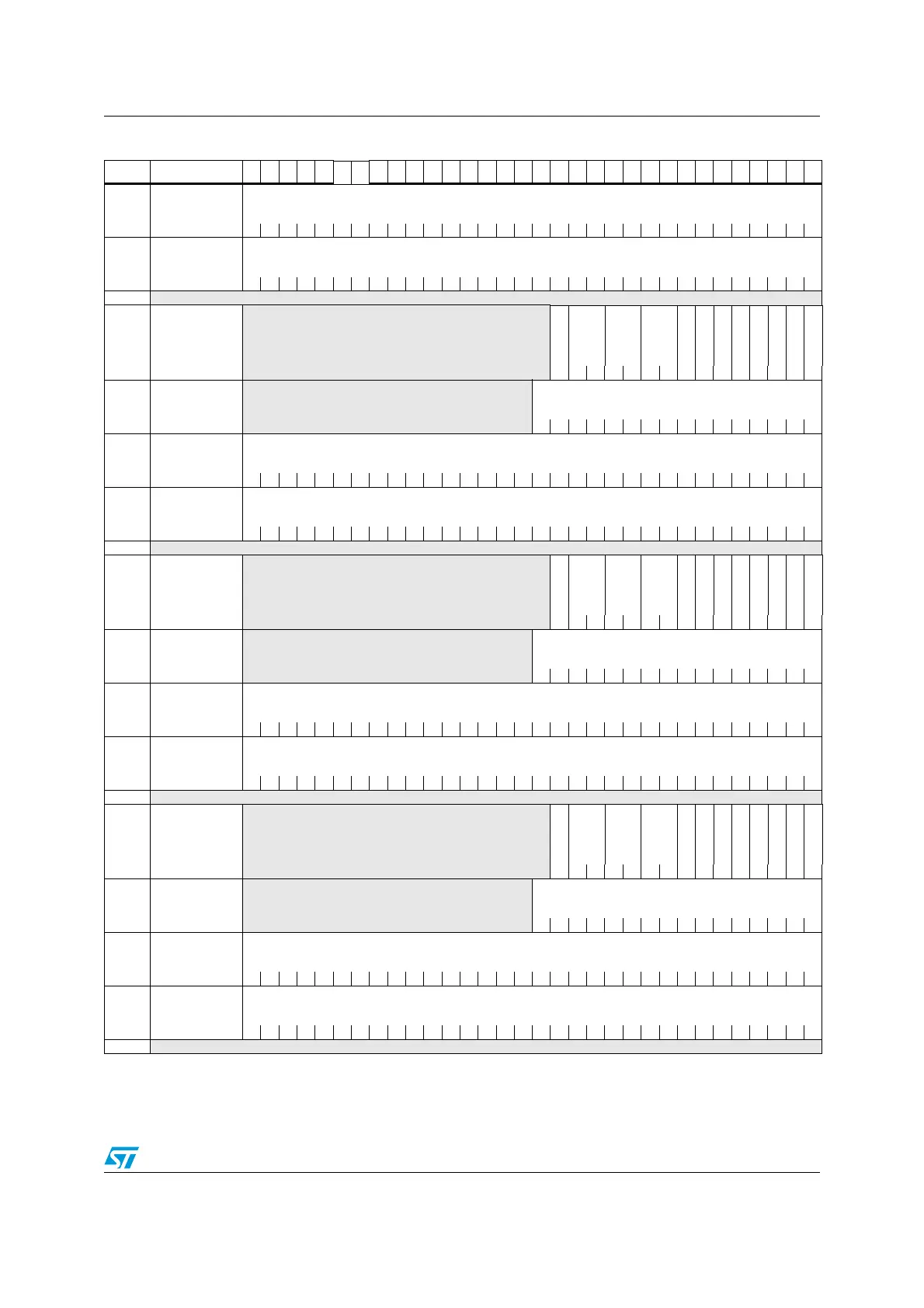

UM0306 DMA controller (DMA)

119/519

024h

DMA_CPAR2 PA[31:0]

Reset Value 00000000000000000000000000000000

028h

DMA_CMAR2 MA[31:0]

Reset Value 00000000000000000000000000000000

02Ch

Reserved

030h

DMA_CCR3

Reserved

MEM2MEM

PL

[1:0]

M

SIZE

[1:0]

PSIZE

[1:0]

MINC

PINC

CIRC

DIR

TEIE

HTIE

TCIE

EN

Reset Value 000000000000000

034h

DMA_CNDTR3

Reserved

NDT[15:0]

Reset Value 0000000000000000

038h

DMA_CPAR3 PA[31:0]

Reset Value 00000000000000000000000000000000

03Ch

DMA_CMAR3 MA[31:0]

Reset Value 00000000000000000000000000000000

040h

Reserved

044h

DMA_CCR4

Reserved

MEM2MEM

PL

[1:0]

M

SIZE

[1:0]

PSIZE

[1:0]

MINC

PINC

CIRC

DIR

TEIE

HTIE

TCIE

EN

Reset Value 000000000000000

048h

DMA_CNDTR4

Reserved

NDT[15:0]

Reset Value 0000000000000000

04Ch

DMA_CPAR4 PA[31:0]

Reset Value 00000000000000000000000000000000

050h

DMA_CMAR4 MA[31:0]

Reset Value 00000000000000000000000000000000

054h

Reserved

058h

DMA_CCR5

Reserved

MEM2MEM

PL

[1:0]

M

SIZE

[1:0]

PSIZE

[1:0]

MINC

PINC

CIRC

DIR

TEIE

HTIE

TCIE

EN

Reset Value 000000000000000

05Ch

DMA_CNDTR5

Reserved

NDT[15:0]

Reset Value 0000000000000000

060h

DMA_CPAR5 PA[31:0]

Reset Value 00000000000000000000000000000000

064h

DMA_CMAR5 MA[31:0]

Reset Value 00000000000000000000000000000000

068h

Reserved

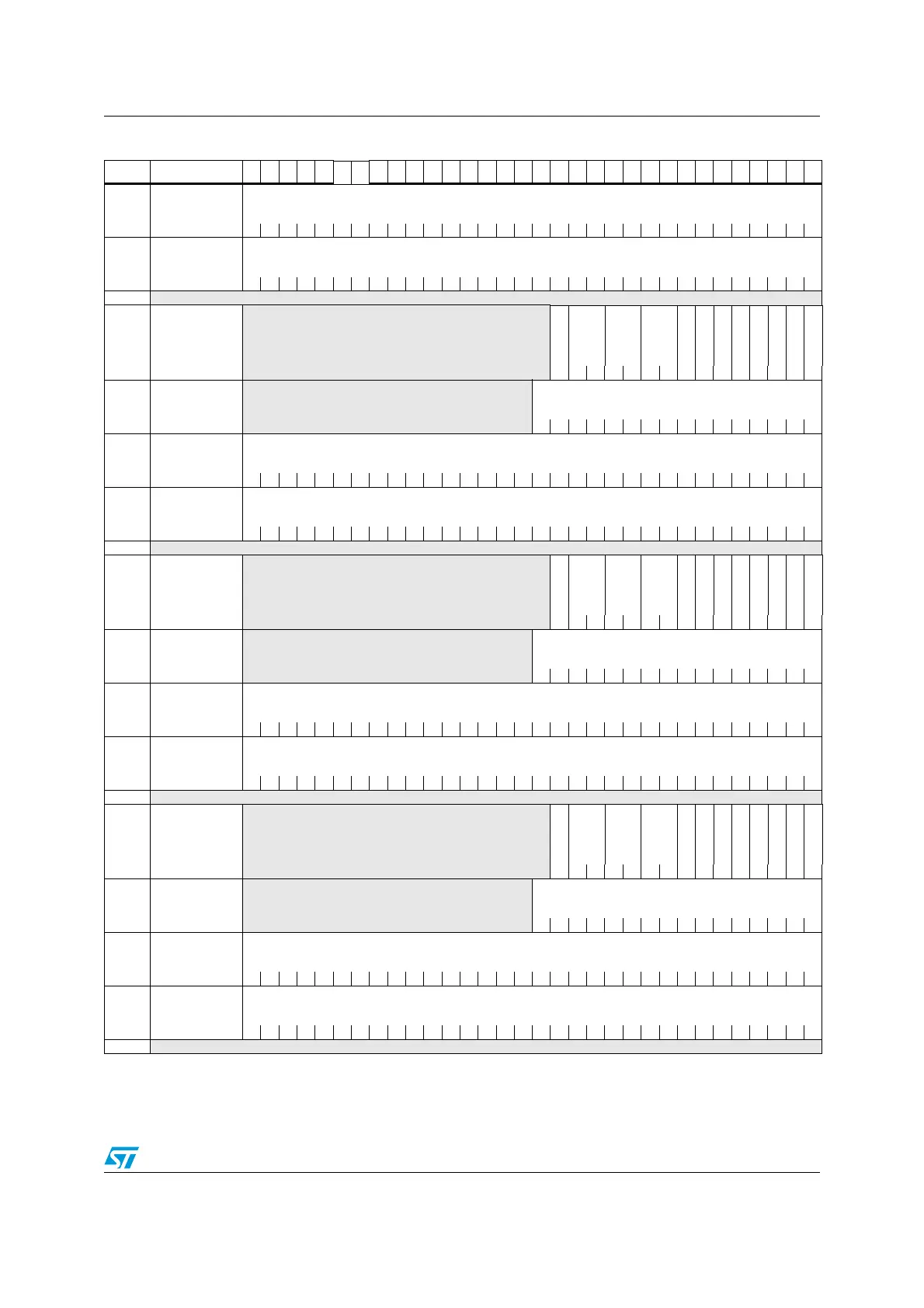

Table 30. DMA - register map and reset values (continued)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...