General purpose timer (TIMx) UM0306

276/519

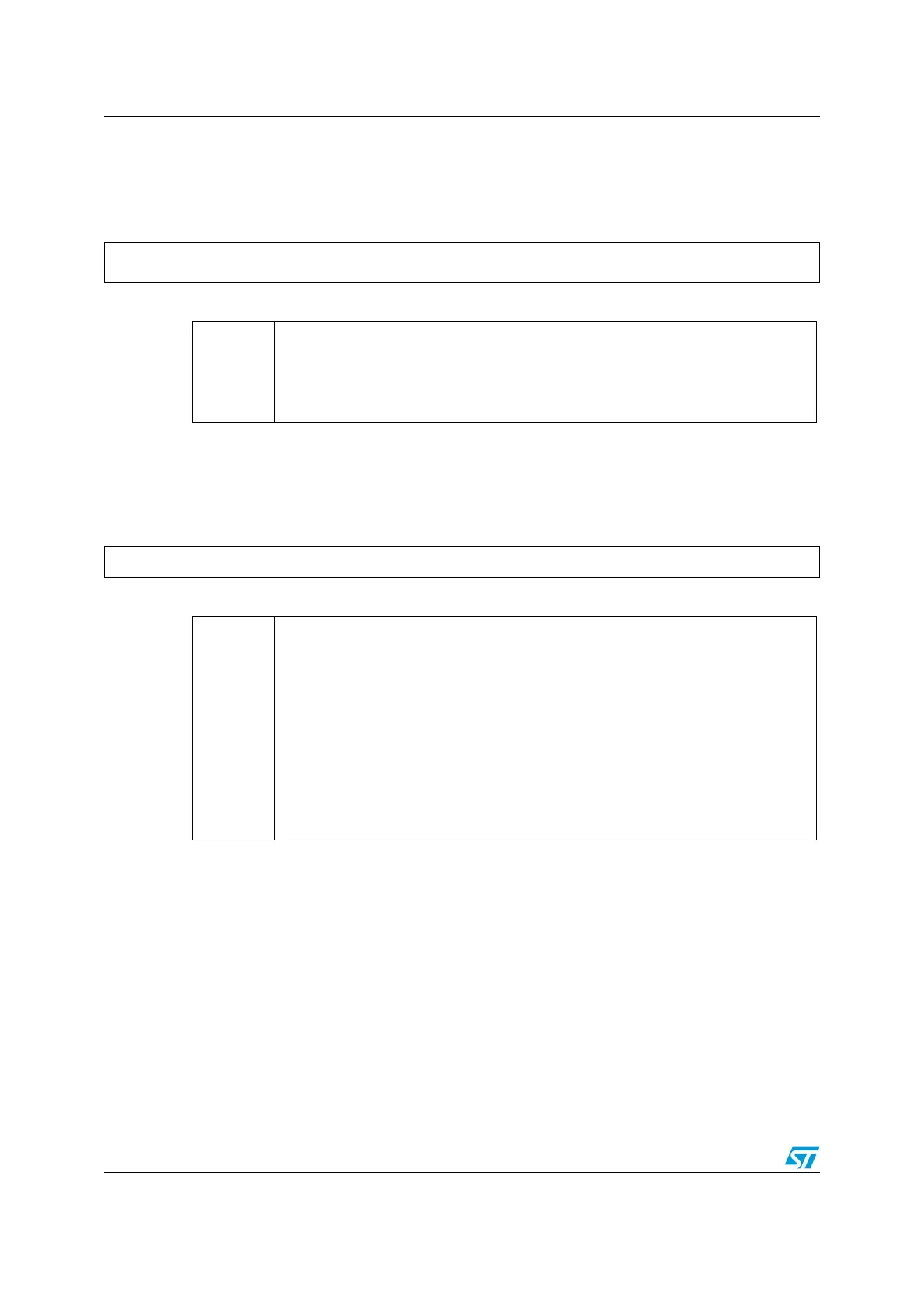

13.5.12 Auto-reload register (TIMx_ARR)

Address offset: 2Ch

Reset value: 0000h

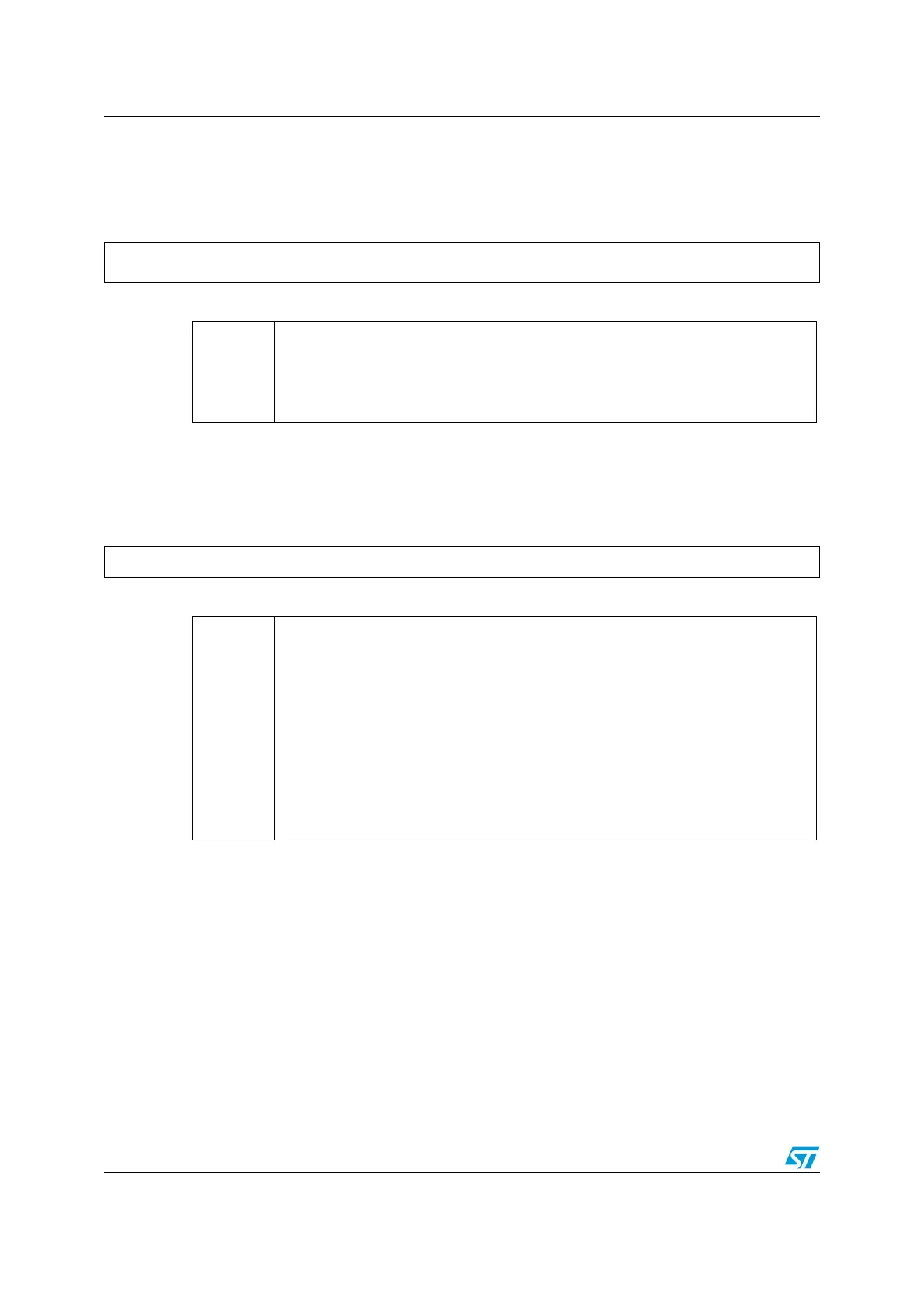

13.5.13 Capture/compare register 1 (TIMx_CCR1)

Address offset: 34h

Reset value: 0000h

1514131211109876543210

ARR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0

ARR[15:0]: Prescaler Value.

ARR is the value to be loaded in the actual auto-reload register.

Refer to the Section 13.4.1: Time base unit on page 222 for more details about ARR

update and behavior.

The counter is blocked while the auto-reload value is null.

1514131211109876543210

CCR1[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 15:0

CCR1[15:0]: Capture/Compare 1 Value).

If channel CC1 is configured as output:

CCR1 is the value to be loaded in the actual capture/compare 1 register (preload

value).

It is loaded permanently if the preload feature is not selected in the TIMx_CCMR1

register (bit OC1PE). Else the preload value is copied in the active capture/compare 1

register when an update event occurs.

The active capture/compare register contains the value to be compared to the counter

TIMx_CNT and signaled on OC1 output.

If channel CC1is configured as input:

CCR1 is the counter value transferred by the last input capture 1 event (IC1).

Loading...

Loading...