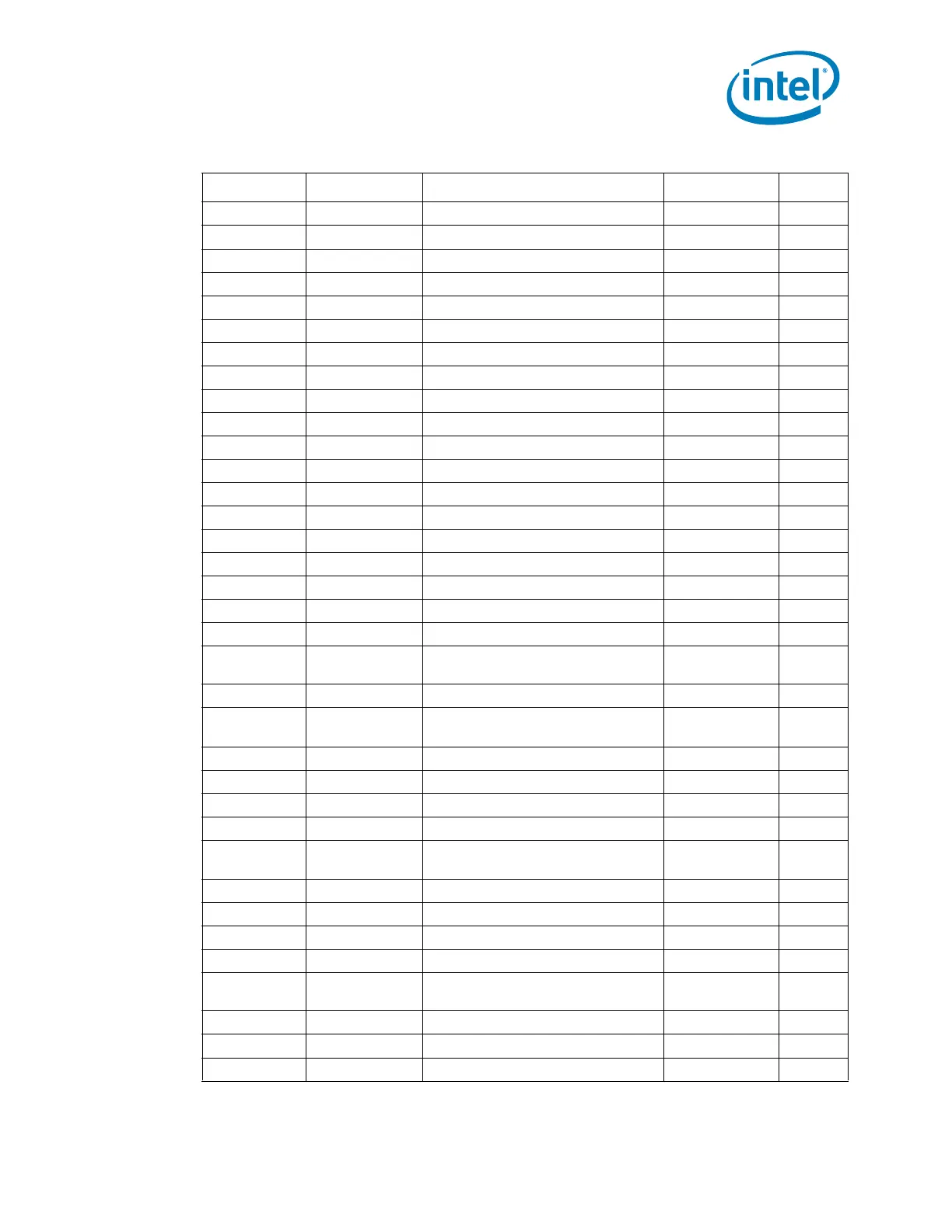

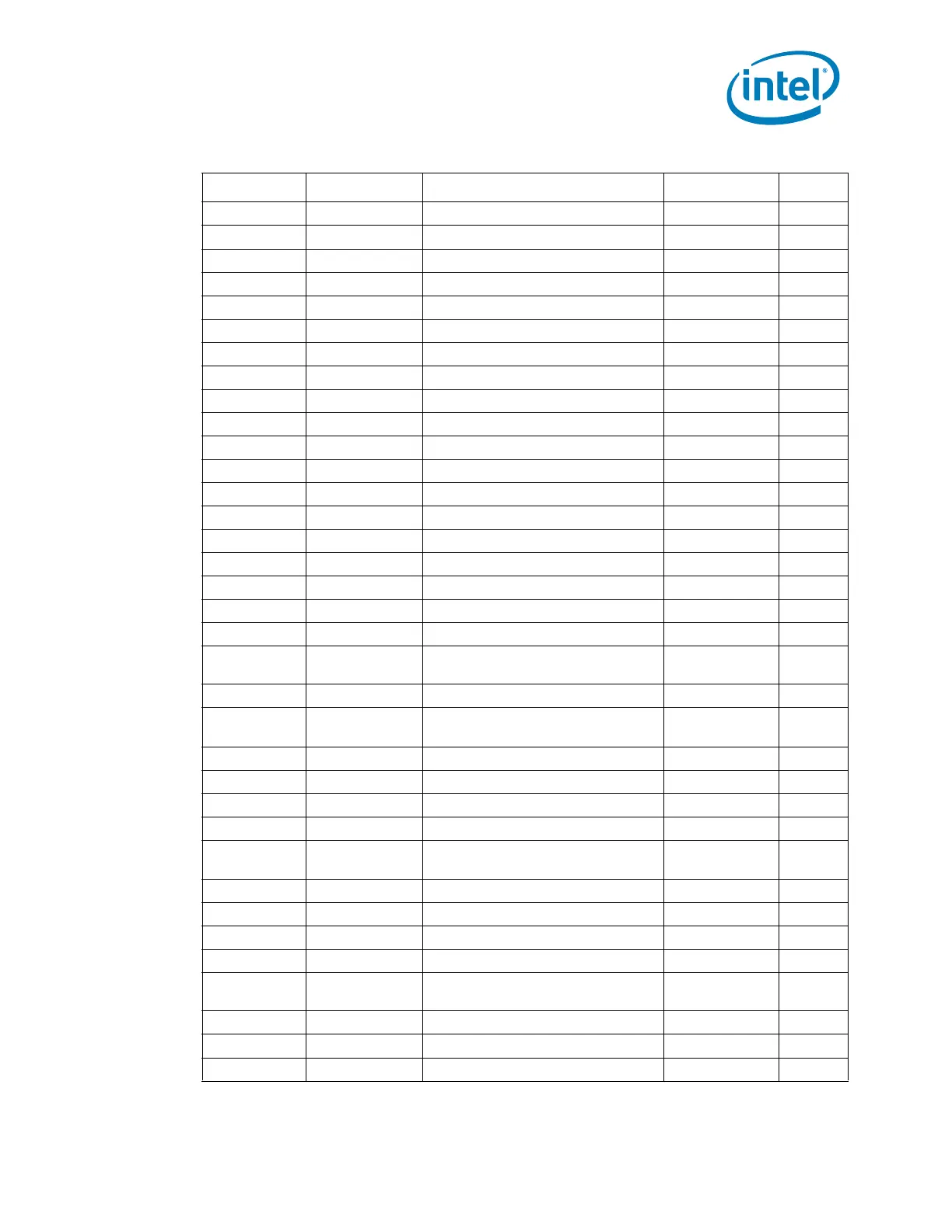

Datasheet 361

Chipset Configuration Registers

3314h–3317h CIR7 Chipset Initialization Register 7 00000000h R/W

3318h–331Bh PM_CFG Power Management Configuration 00000000h R/W

3324h–3327h CIR8 Chipset Initialization Register 8 00000000h R/W

332Ch–332Fh DEEP_S4_POL Deep S4 Power Policies 00000000h R/W

3330h–3333h DEEP_S5_POL Deep S5 Power Policies 00000000h R/W

3340h–3343h CIR10 Chipset Initialization Register 10 00000000h R/W

3344h–3347h CIR11 Chipset Initialization Register 11 00000000h R/W

3360h–3363h CIR12 Chipset Initialization Register12 00000000h R/W

3368h–336Bh CIR14 Chipset Initialization Register 14 00000000h R/W

3378h–337Bh CIR15 Chipset Initialization Register 15 00000000h R/W

337Ch–337Fh CIR13 Chipset Initialization Register 13 00000000h R/W

3388h–338Bh CIR16 Chipset Initialization Register 16 00000000h R/W

3390h–3393h CIR18 Chipset Initialization Register 18 00000000h R/W

33A0h–33A3h CIR17 Chipset Initialization Register 17 00000000h R/W

33B0h–33B3h CIR23 Chipset Initialization Register 23 00000000h R/W

33C0h–33C3h CIR19 Chipset Initialization Register 19 00000000h R/W

33CCh–33CFh CIR20 Chipset Initialization Register 20 00000000h R/W

33D0h–33D3h CIR21 Chipset Initialization Register 21 00000000h R/W

33D4h–33D7h CIR22 Chipset Initialization Register 22 00000000h R/W

3400h–3403h RC RTC Configuration 00000000h

R/W,

R/WLO

3404h–3407h HPTC High Precision Timer Configuration 00000000h R/W

3410h–3413h GCS General Control and Status 000000yy0h

R/W,

R/WLO

3414h–3414h BUC Backed Up Control 00h R/W

3418h–341Bh FD Function Disable 00000000h R/W

341Ch–341Fh CG Clock Gating 00000000h R/W

3420h–3420h FDSW Function Disable SUS Well 00h R/W

3424h–3425h DISPBDF

Display Bus, Device and Function

Initialization

0010h R/W

3428h–342Bh FD2 Function Disable 2 00000000h R/W

3590h–3594h MISCCTL Miscellaneous Control Register 00000000h R/W

35A0h–35A3h USBOCM1 USB Overcurrent MAP Register 1 00000000h R/WO

35A4h–35A7h USBOCM2 USB Overcurrent MAP Register 2 00000000h R/WO

35B0h–35B3h RMHWKCTL

USB Rate Matching Hub Wake

Control

00000000h R/WO

3A28

–3A2Bh CIR24 Chipset Initialization Register 24 00000000h R/W

3A2C–3A2Fh CIR25 Chipset Initialization Register 25 00000000h R/W

3A6C–3A6Fh CIR26 Chipset Initialization Register 26 00000000h R/W

Table 10-1. Chipset Configuration Register Memory Map (Memory Space) (Sheet 3 of 4)

Offset Mnemonic Register Name Default Type

Loading...

Loading...