Datasheet 693

Integrated Intel

®

High Definition Audio Controller Registers

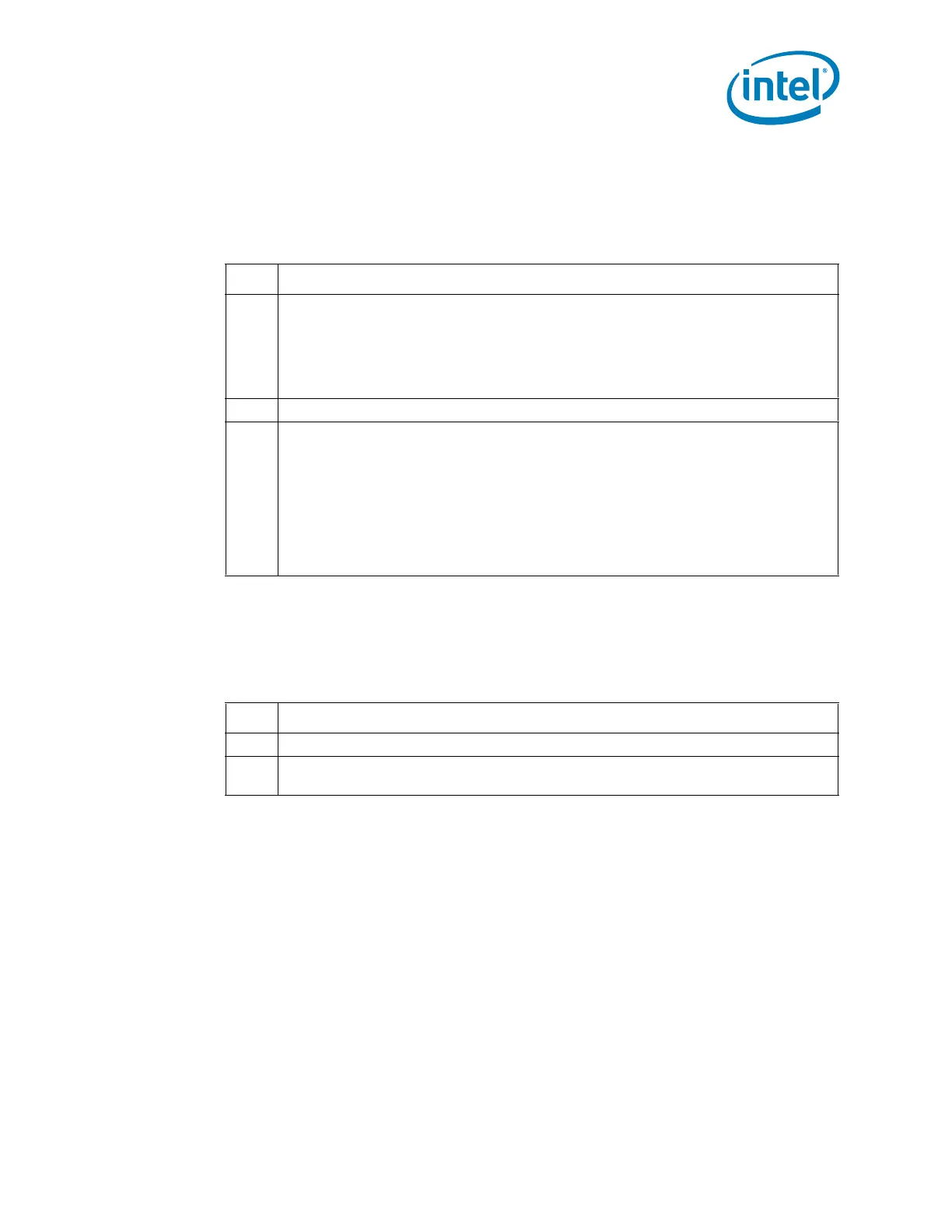

17.1.1.22 DCKSTS—Docking Status Register (Mobile Only)

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 4Dh Attribute: R/WO, RO

Default Value: 80h Size: 8 bits

Function Level Reset: No

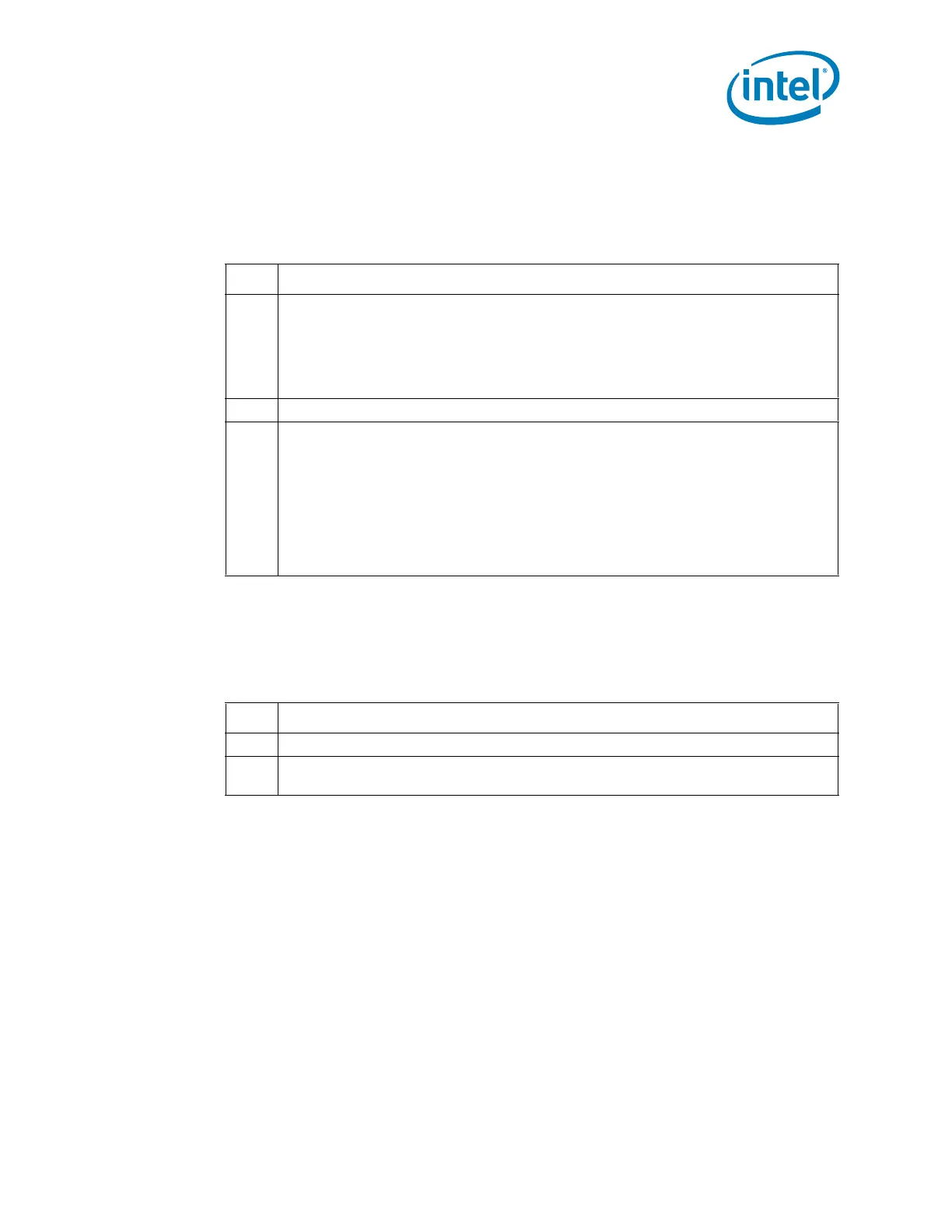

17.1.1.23 PID—PCI Power Management Capability ID Register

(Intel

®

High Definition Audio Controller—D27:F0)

Address Offset: 50h–51h Attribute: R/WO, RO

Default Value: 6001h Size: 16 bits

Function Level Reset: No (Bits 7:0 only)

Bit Description

7

Docking Supported (DS) — R/WO: A 1 indicates that PCH supports HD Audio

Docking. The DCKCTL.DA bit is only writable when this DS bit is 1. ACPI BIOS software

should only branch to the docking routine when this DS bit is 1. BIOS may clear this bit

to 0 to prohibit the ACPI BIOS software from attempting to run the docking routines.

Note that this bit is reset to its default value only on a PLTRST#, but not on a CRST# or

D3hot-to-D0 transition.

6:1 Reserved.

0

Dock Mated (DM) — RO: This bit effectively communicates to software that an Intel

®

HD Audio docked codec is physically and electrically attached.

Controller hardware sets this bit to 1 after the docking sequence triggered by writing a

1 to the Dock Attach (GCTL.DA) bit is completed (HDA_DOCK_RST# deassertion). This

bit indicates to software that the docked codec(s) may be discovered using the

STATESTS register and then enumerated.

Controller hardware sets this bit to 0 after the undocking sequence triggered by writing

a 0 to the Dock Attach (GCTL.DA) bit is completed (HDA_DOCK_EN# deasserted). This

bit indicates to software that the docked codec(s) may be physically undocked.

Bit Description

15:8 Next Capability (Next) — R/WO. Points to the next capability structure (MSI).

7:0

Cap ID (CAP) — RO. Hardwired to 01h. Indicates that this pointer is a PCI power

management capability. These bits are not reset by Function Level Reset.

Loading...

Loading...