SMBus Controller Registers (D31:F3)

744 Datasheet

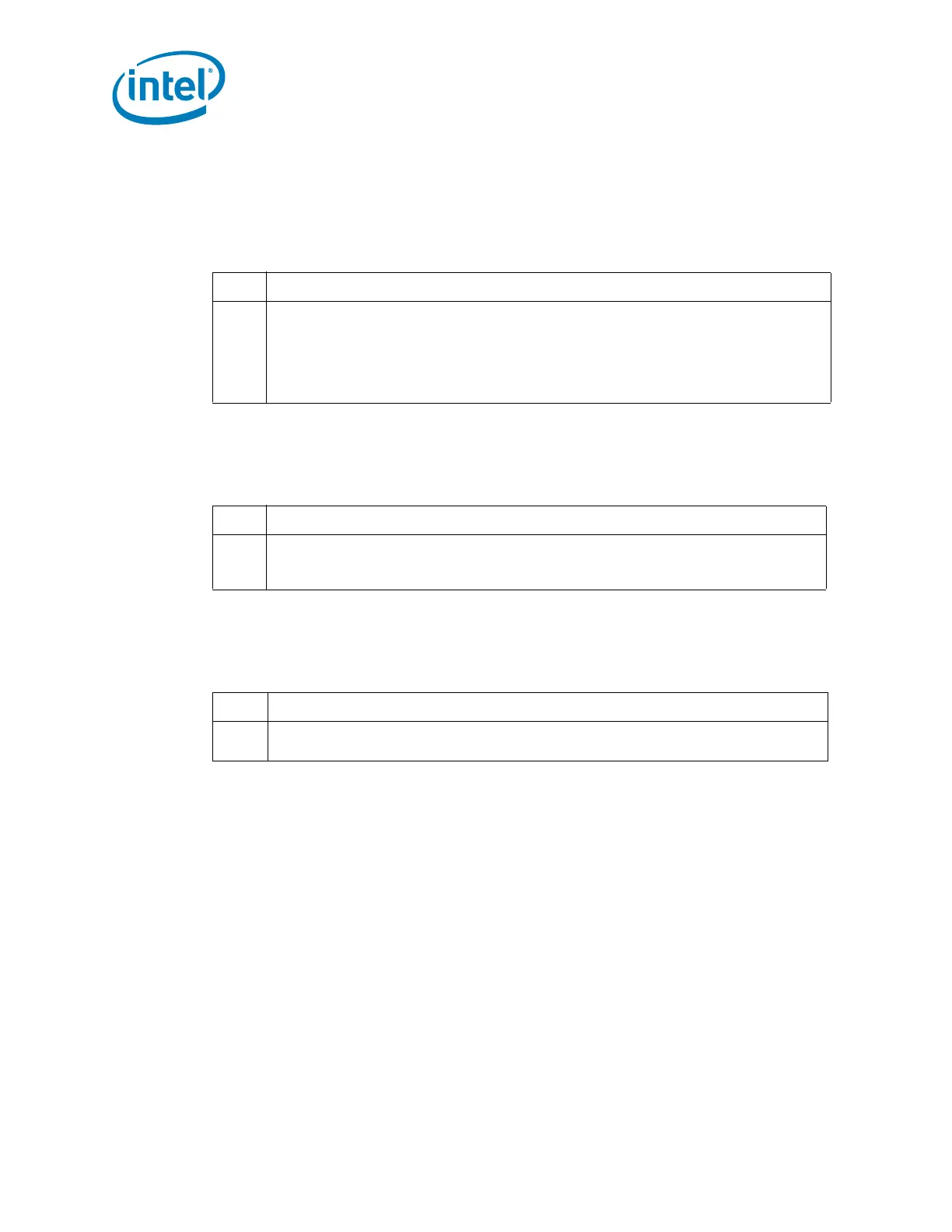

18.1.13 SID—Subsystem Identification Register

(SMBus—D31:F2/F4)

Address Offset: 2Eh–2Fh Attribute: R/WO

Default Value: 0000h Size: 16 bits

Lockable: No Power Well: Core

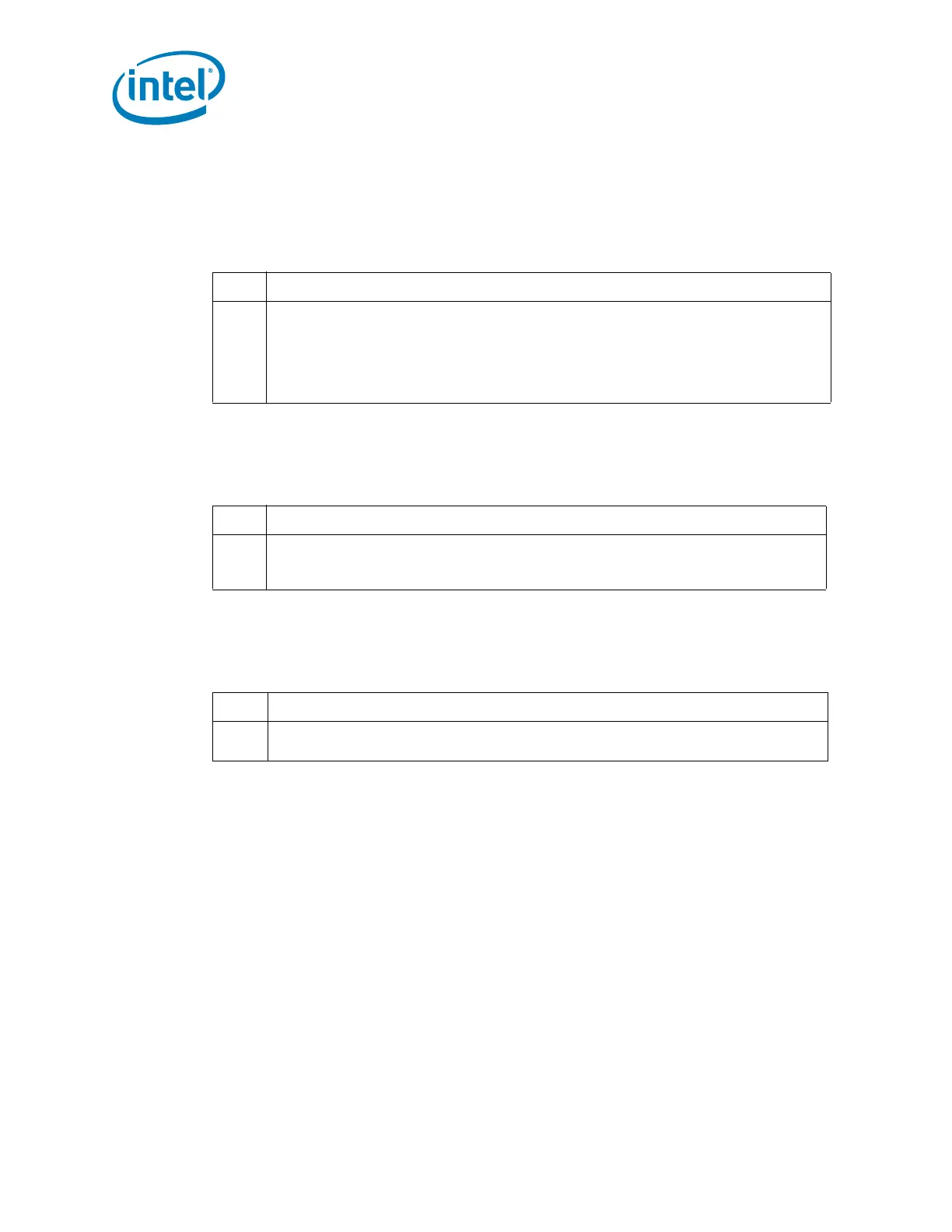

18.1.14 INT_LN—Interrupt Line Register (SMBus—D31:F3)

Address Offset: 3Ch Attributes: R/W

Default Value: 00h Size: 8 bits

18.1.15 INT_PN—Interrupt Pin Register (SMBus—D31:F3)

Address Offset: 3Dh Attributes: RO

Default Value: See description Size: 8 bits

Bit Description

15:0

Subsystem ID (SID) — R/WO. The SID register, in combination with the SVID register,

enables the operating system (OS) to distinguish subsystems from each other. The

value returned by reads to this register is the same as that which was written by BIOS

into the IDE SID register.

NOTE: Software can write to this register only once per core well reset. Writes should

be done as a single 16-bit cycle.

Bit Description

7:0

Interrupt Line (INT_LN) — R/W. This data is not used by the PCH. It is to

communicate to software the interrupt line that the interrupt pin is connected to

PIRQB#.

Bit Description

7:0

Interrupt PIN (INT_PN) — RO. This reflects the value of D31IP.SMIP in chipset

configuration space.

Loading...

Loading...