SMBus Controller Registers (D31:F3)

754 Datasheet

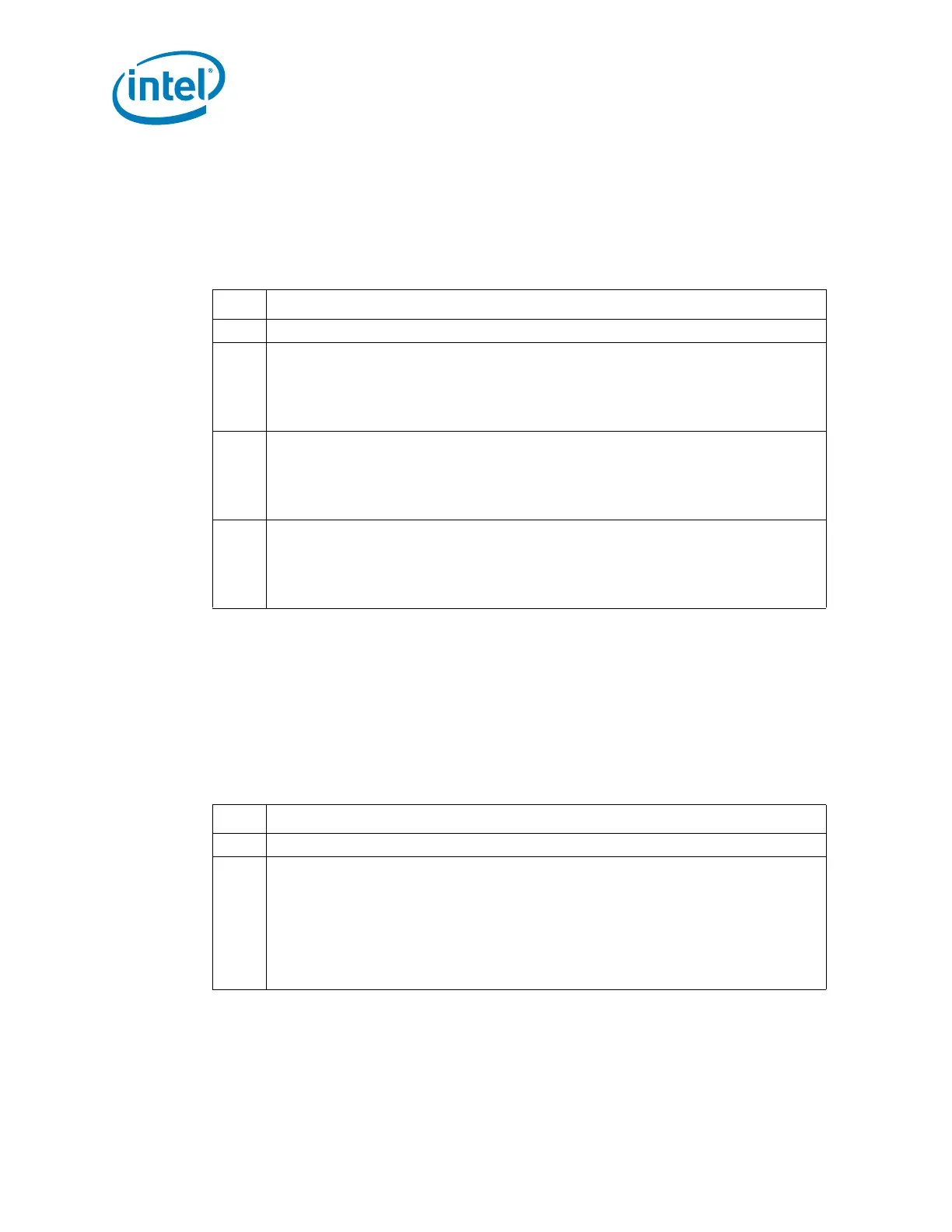

18.2.14 SMBus_PIN_CTL—SMBus Pin Control Register

(SMBus—D31:F3)

Register Offset: SMB_BASE + 0Fh Attribute: R/W, RO

Default Value: See below Size: 8 bits

Note: This register is in the resume well and is reset by RSMRST#.

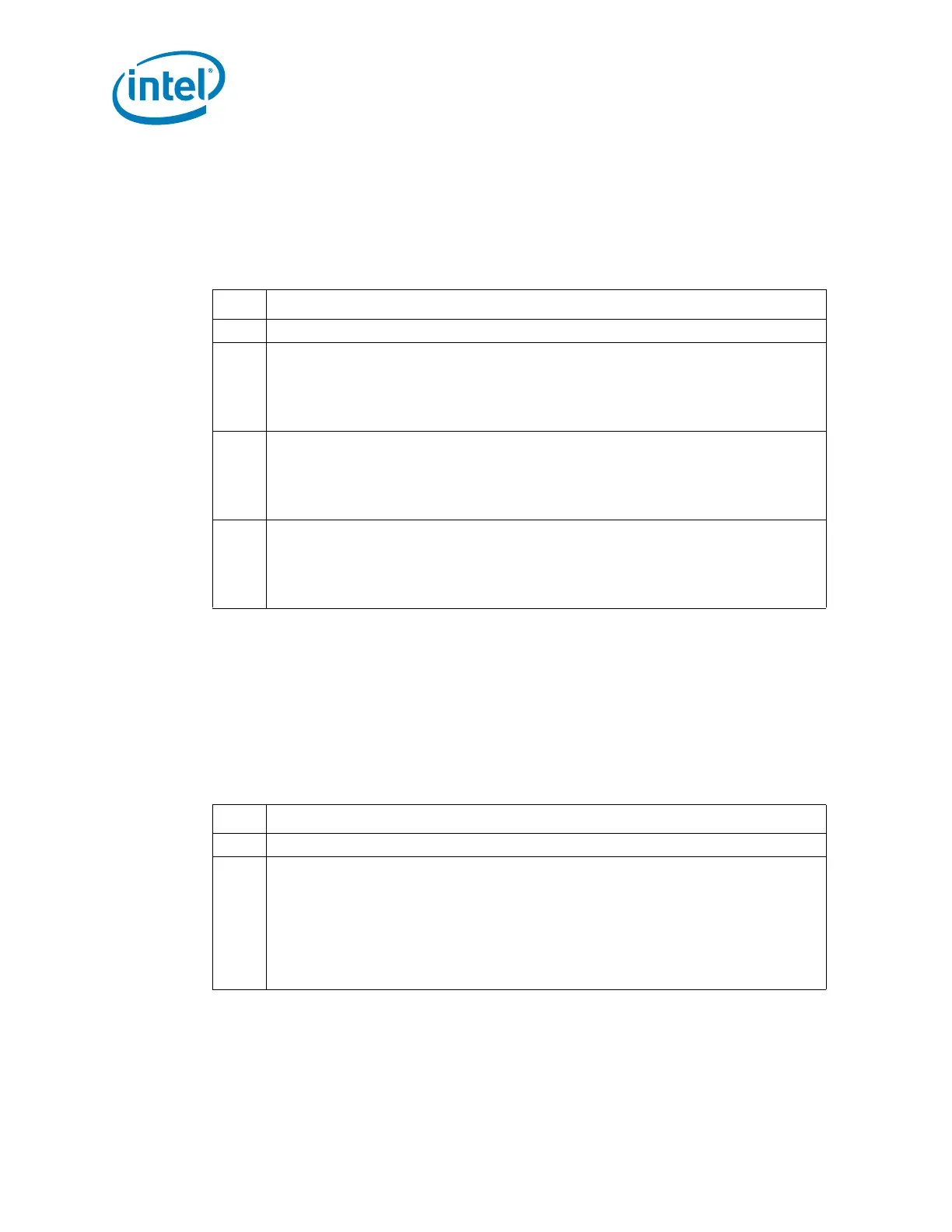

18.2.15 SLV_STS—Slave Status Register (SMBus—D31:F3)

Register Offset: SMB_BASE + 10h Attribute: R/WC

Default Value: 00h Size: 8 bits

Note: This register is in the resume well and is reset by RSMRST#.

All bits in this register are implemented in the 64 kHz clock domain. Therefore,

software must poll this register until a write takes effect before assuming that a write

has completed internally.

Bit Description

7:3 Reserved

2

SMBCLK_CTL — R/W.

1 = The SMBCLK pin is not overdriven low. The other SMBus logic controls the state of

the pin.

0 = The PCH drives the SMBCLK pin low, independent of what the other SMB logic

would otherwise indicate for the SMBCLK pin. (Default)

1

SMBDATA_CUR_STS — RO. This read-only bit has a default value that is dependent

on an external signal level. This pin returns the value on the SMBDATA pin. This allows

software to read the current state of the pin.

0 = Low

1 = High

0

SMBCLK_CUR_STS — RO. This read-only bit has a default value that is dependent on

an external signal level. This pin returns the value on the SMBCLK pin. This allows

software to read the current state of the pin.

0 = Low

1 = High

Bit Description

7:1 Reserved

0

HOST_NOTIFY_STS — R/WC. The PCH sets this bit to a 1 when it has completely

received a successful Host Notify Command on the SMBus pins. Software reads this bit

to determine that the source of the interrupt or SMI# was the reception of the Host

Notify Command. Software clears this bit after reading any information needed from

the Notify address and data registers by writing a 1 to this bit. Note that the PCH will

allow the Notify Address and Data registers to be over-written once this bit has been

cleared. When this bit is 1, the PCH will NACK the first byte (host address) of any new

“Host Notify” commands on the SMBus pins. Writing a 0 to this bit has no effect.

Loading...

Loading...