Datasheet 859

Thermal Sensor Registers (D31:F6)

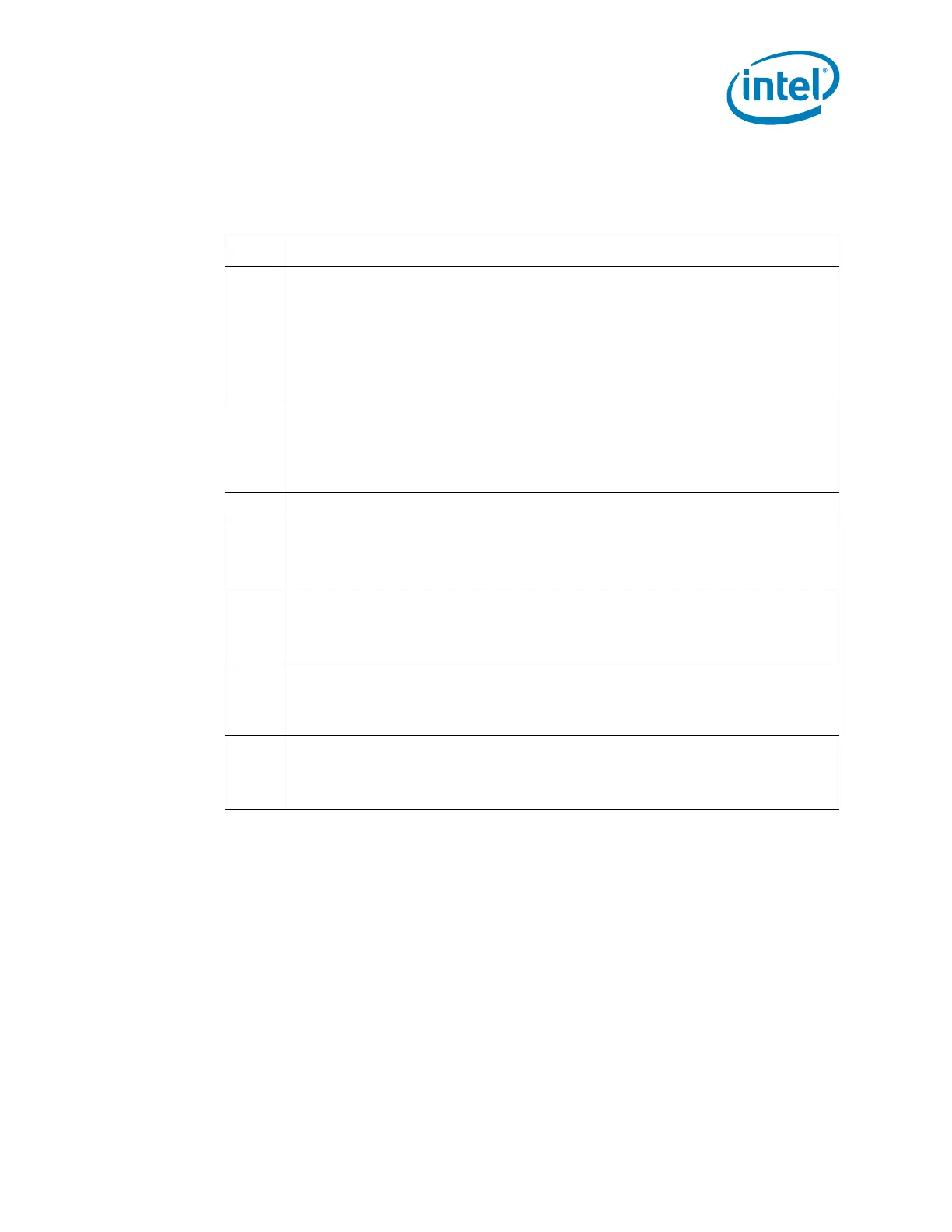

22.2.9 TSPC—Thermal Sensor Policy Control

Offset Address: TBARB+0Eh Attribute: R/W, RO

Default Value: 00h Size: 8 bit

Bit Description

7

Policy Lock-Down Bit — R/W.

0 = This register can be programmed and modified.

1 = Prevents writes to this register and TSTTP.bits [31:16] (offset 04h).

NOTE: TSCO.bit 7 (offset 08h) and TSLOCK.bit2 (offset 83h) must also be 1 when this

bit is set to 1.

This bit is reset to 0 by a host partitioned reset (note that CF9 warm reset is a host

partitioned reset). Writing a 0 to this bit has no effect.

6

Catastrophic Power-Down Enable — R/W.

When set to 1, the power management logic unconditionally transitions to the S5 state

when a catastrophic temperature is detected by the sensor.

NOTE: BIOS should set this bit to 1 to enable Catastrophic power-down.

5:4 Reserved

3

SMI Enable on Auxiliary2 Thermal Sensor Trip — R/W.

0 = Disables SMI# assertion for Auxiliary2 Thermal Sensor events.

1 = Enables SMI# assertions on Auxiliary2 Thermal Sensor events for either low-to-

high or high-to-low events. (Both edges are enabled by this bit.)

2

SMI Enable on Catastrophic Thermal Sensor Trip — R/W.

0 = Disables SMI# assertion for Catastrophic Thermal Sensor events.

1 = Enables SMI# assertions on Catastrophic Thermal Sensor events for either low-to-

high or high-to-low events. (Both edges are enabled by this bit.)

1

SMI Enable on Hot Thermal Sensor Trip — R/W.

0 = Disables SMI# assertion for Hot Thermal Sensor events.

1 = Enables SMI# assertions on Hot Thermal Sensor events for either low-to-high or

high-to-low events. (Both edges are enabled by this bit.)

0

SMI Enable on Auxiliary Thermal Sensor Trip — R/W.

0 = Disables SMI# assertion for Auxiliary Thermal Sensor events.

1 = Enables SMI# assertions on Auxiliary Thermal Sensor events for either low-to-

high or high-to-low events. (Both edges are enabled by this bit.)

Loading...

Loading...