Datasheet 881

Intel® Management Engine Interface (MEI) Subsystem Registers (D22:F0)

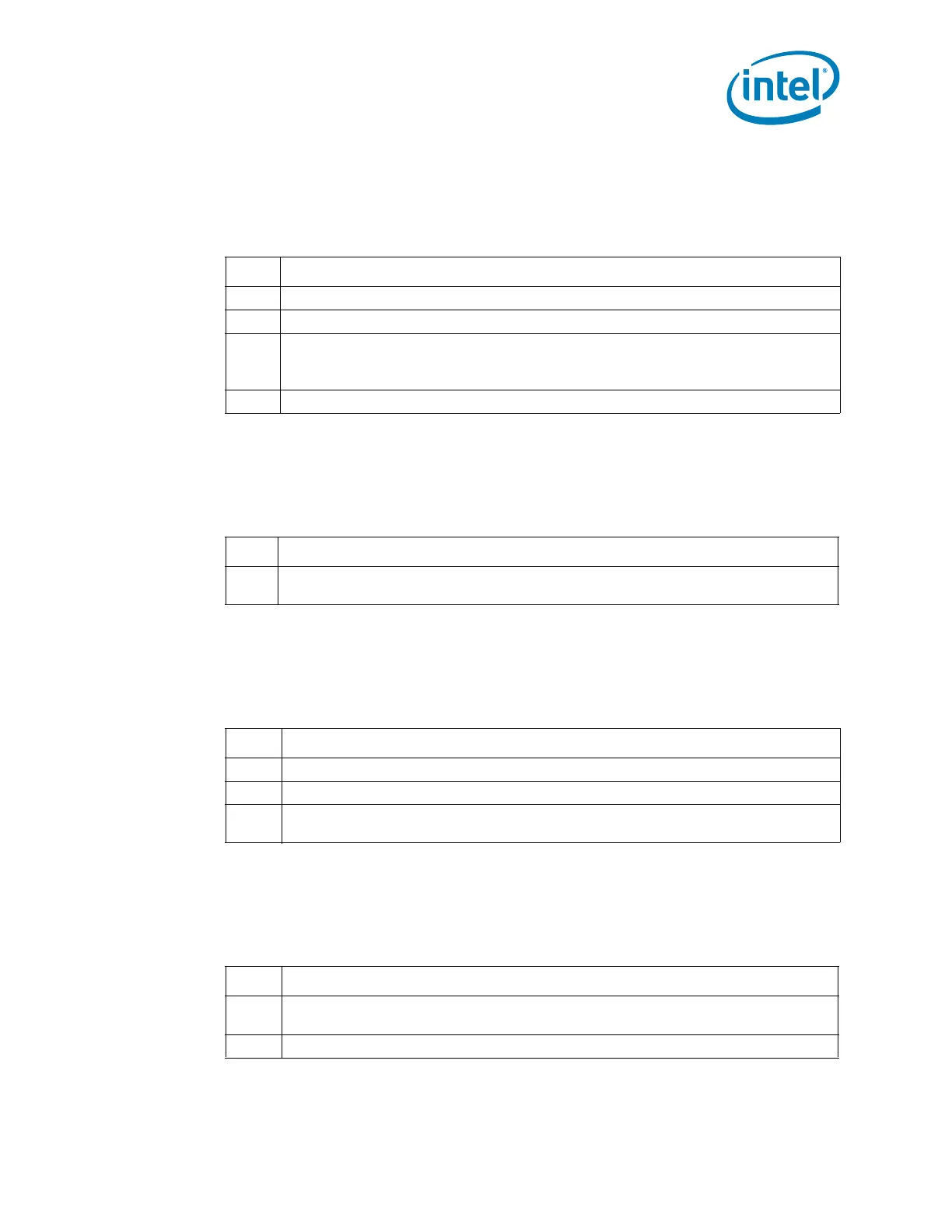

23.2.4 PCISTS—PCI Status Register

(MEI—D22:F1)

Address Offset: 06h–07h Attribute: RO

Default Value: 0010h Size: 16 bits

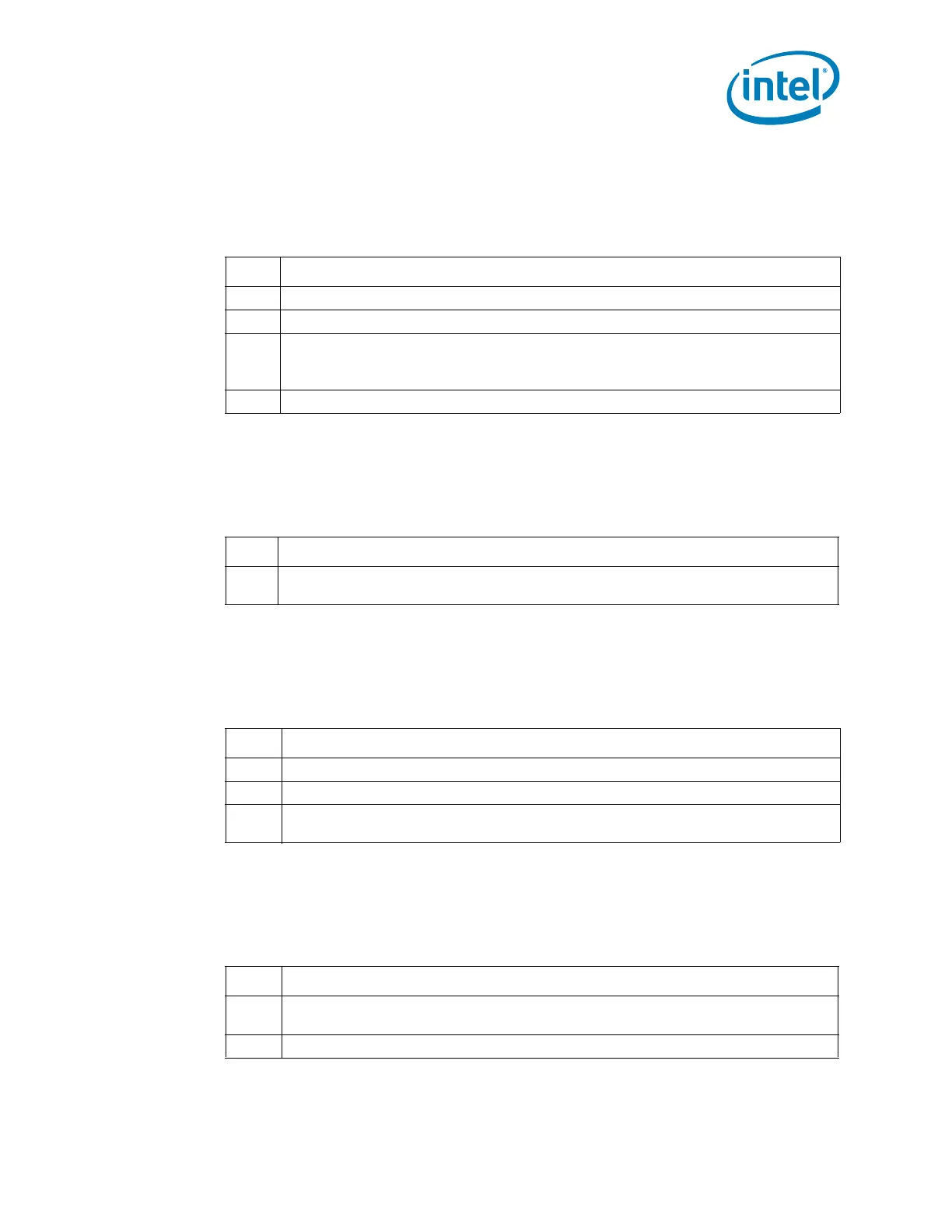

23.2.5 RID—Revision Identification Register

(MEI—D22:F1)

Offset Address: 08h Attribute: RO

Default Value: See bit description Size: 8 bits

23.2.6 CC—Class Code Register

(MEI—D22:F1)

Address Offset: 09h–0Bh Attribute: RO

Default Value: 078000h Size: 24 bits

23.2.7 HTYPE—Header Type Register

(MEI—D22:F1)

Address Offset: 0Eh Attribute: RO

Default Value: 80h Size: 8 bits

Bit Description

15:5 Reserved

4 Capabilities List (CL) — RO. Indicates the presence of a capabilities list, hardwired to 1.

3

Interrupt Status

— RO. Indicates the interrupt status of the device.

0 = Interrupt is deasserted.

1 = Interrupt is asserted.

2:0 Reserved

Bit Description

7:0

Revision ID — RO. See the Intel

®

6 Series Chipset Specification Update for the value

of the RID Register.

Bit Description

23:16 Base Class Code (BCC) — RO. Indicates the base class code of the Intel MEI device.

15:8 Sub Class Code (SCC) — RO. Indicates the sub class code of the Intel MEI device.

7:0

Programming Interface (PI) — RO. Indicates the programming interface of the Intel

MEI device.

Bit Description

7

Multi-Function Device (MFD) — RO. Indicates the Intel MEI host controller is part of

a multifunction device.

6:0 Header Layout (HL) — RO. Indicates that the Intel MEI uses a target device layout.

Loading...

Loading...