Rev. 1.50, 10/04, page 438 of 448

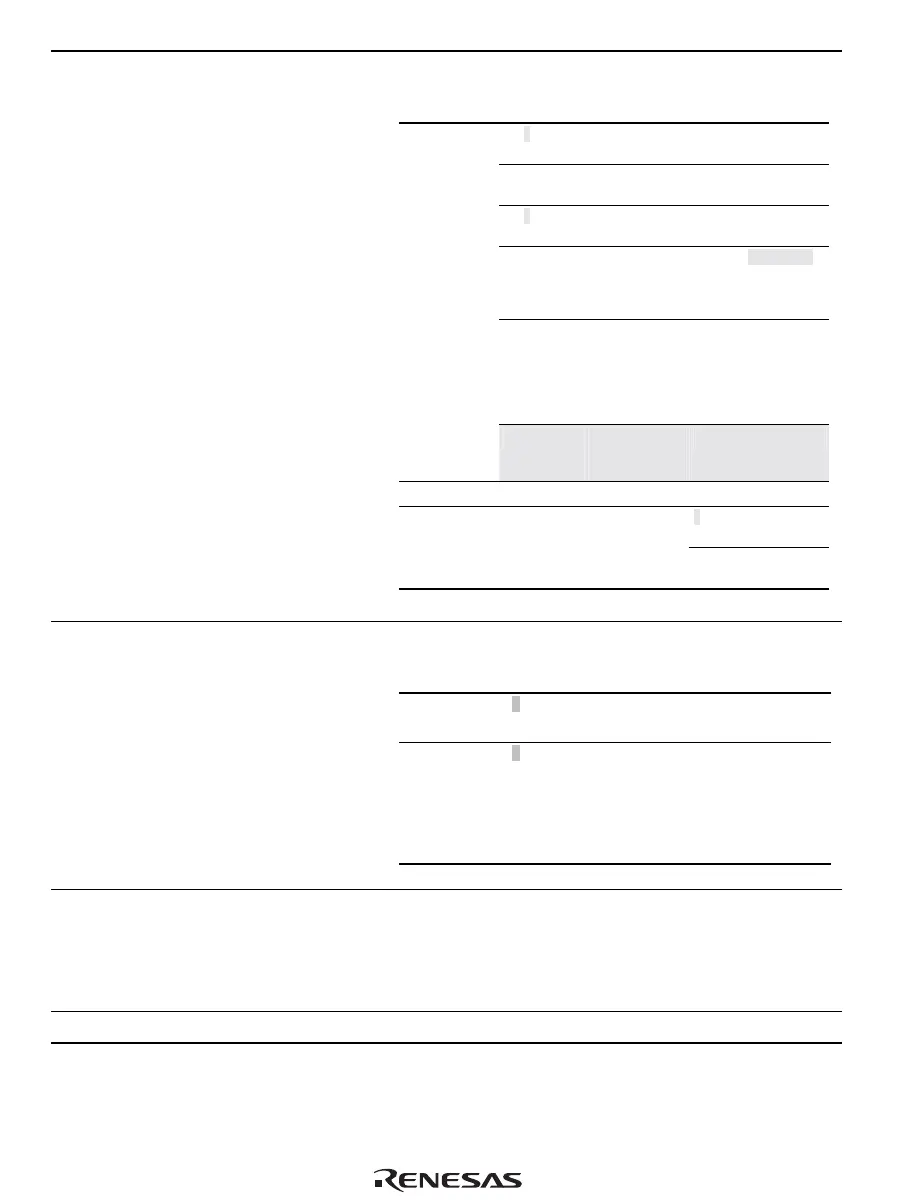

Item Page Revision (See Manual for Details)

Table 1.2 Changes from SH-4 to

SH-4A

6 Added.

Section No. and

Name Sub-section

Sub-section

Name Changes

8.3.6 OC Two-Way

Mode

Newly added.

8.4 Instruction Cache

Operation

IC index mode is

deleted.

8.4.3 IC Two-Way

Mode

Newly added.

8.5.1 Coherency

between Cache

and External

Memory

The ICBI, PREFI, and

SYNCO instructions are

added.

8. Caches

8.6 Memory-Mapped

Cache

Configuration

The entry bits and the

way bits are modified

according to the size

modification and

changed into 4-way set

associative cache.

8.8 Notes on Using

32-Bit Address

Extended Mode

Newly added.

9. L Memory Newly added.

9 instructions are added

as CPU instructions.

10. Instruction

Descriptions

3 instructions are added

as FPU instructions.

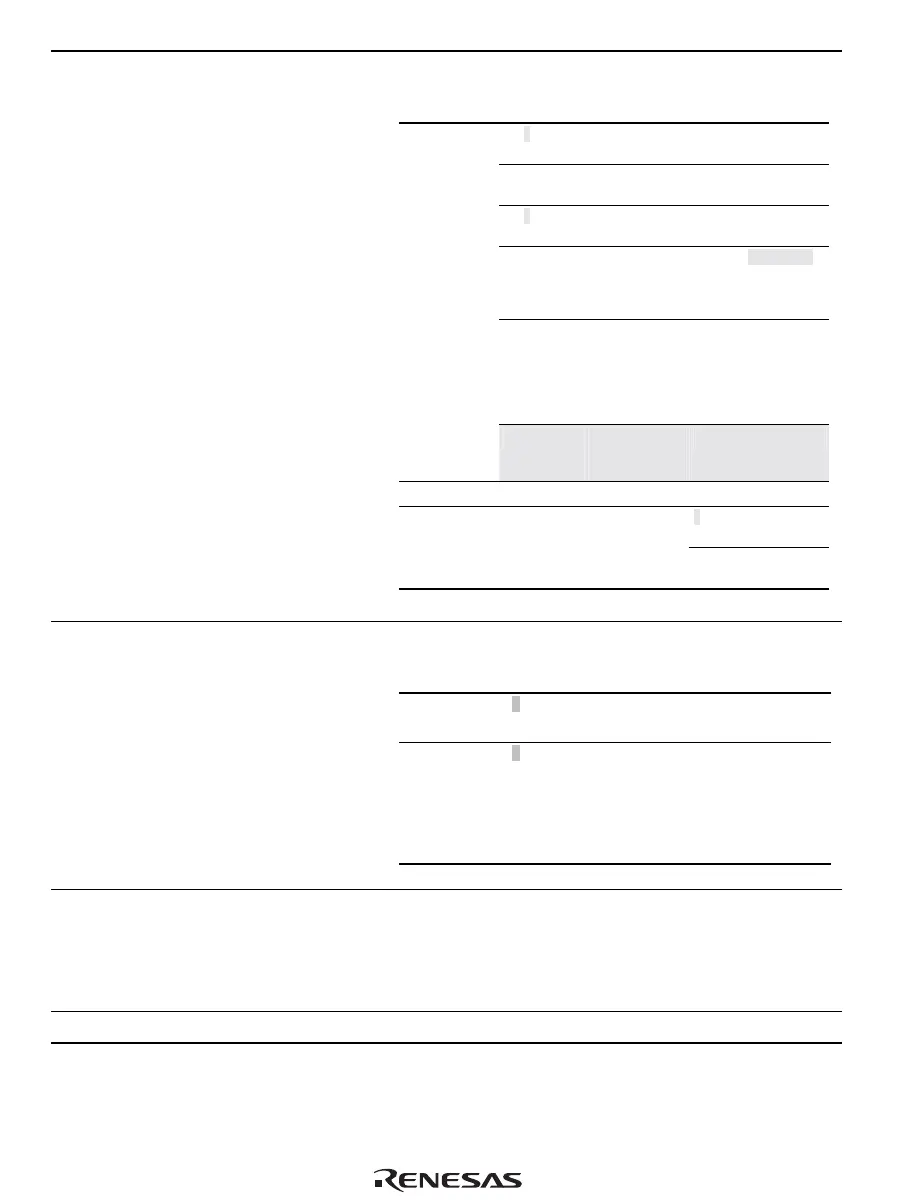

2.2.4 Control Registers

Status Register (SR)

15 Amended.

Bit Bit Name

Initial

Value R/W Description

1 S 0 R/W S Bit

Used by the MAC instruction.

0 T 0 R/W T Bit

Indicates true/false condition,

carry/borrow, or

overflow/underflow.

For details, see section 3,

Instruction Set.

2.2.5 System Registers

Floating-Point Status/Control

Register (FPSCR)

18 Amended.

2.7 Usage Notes 22 Added.

Loading...

Loading...