Rev. 1.50, 10/04, page 28 of 448

Addressing

Mode

Instruction

Format Effective Address Calculation Method

Calculation

Formula

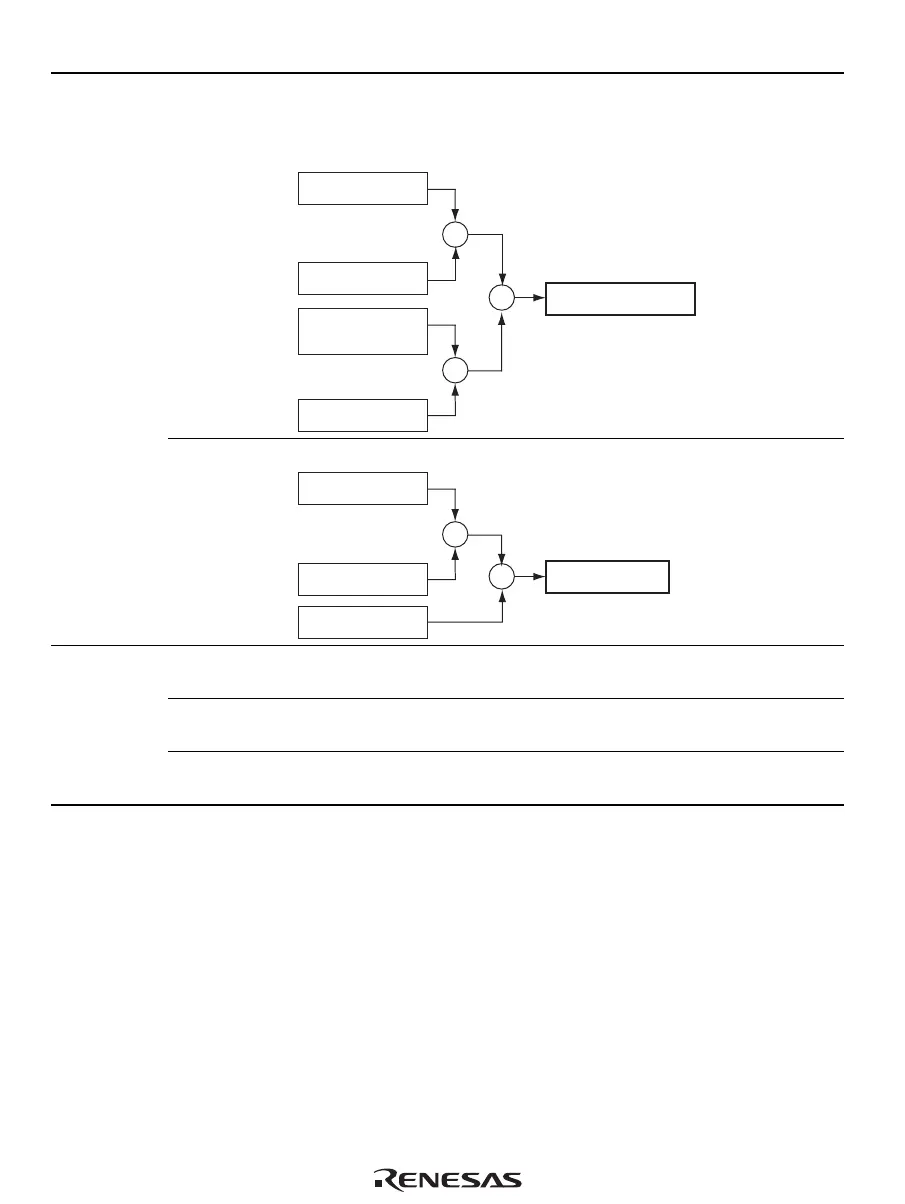

PC-relative disp:12 Effective address is PC + 4 with 12-bit

displacement disp added after being sign-extended

and

multiplied by 2.

2

+

×

disp

(sign-extended)

4

+

PC

PC + 4 + disp × 2

PC + 4 + disp

× 2 → Branch-

Target

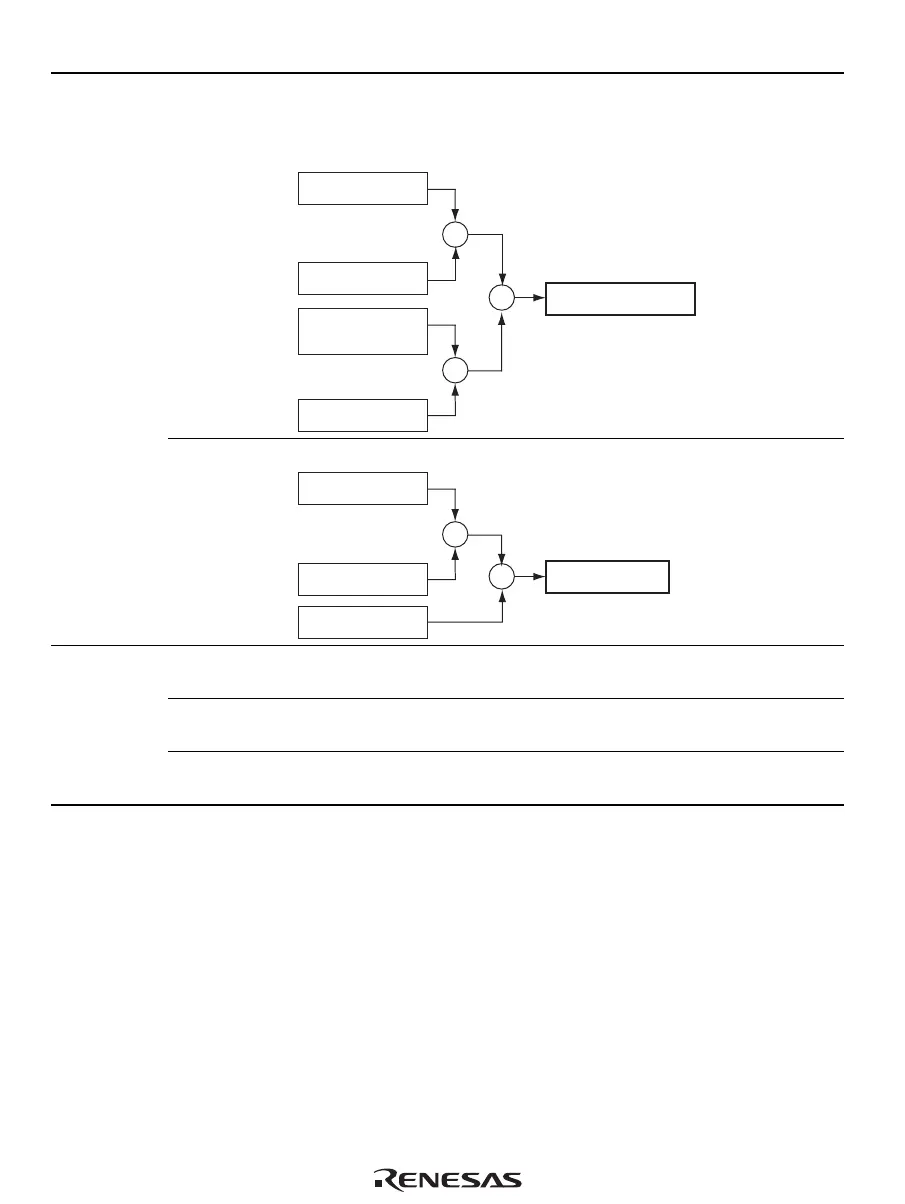

Rn Effective address is sum of PC + 4 and Rn.

PC

4

Rn

+

+

PC + 4 + Rn

PC + 4 + Rn →

Branch-Target

Immediate #imm:8 8-bit immediate data imm of TST, AND, OR, or

XOR instruction is zero-extended.

—

#imm:8 8-bit immediate data imm of MOV, ADD, or

CMP/EQ instruction is sign-extended.

—

#imm:8 8-bit immediate data imm of TRAPA instruction is

zero-extended and multiplied by 4.

—

Note: For the addressing modes below that use a displacement (disp), the assembler descriptions

in this manual show the value before scaling (×1, ×2, or ×4) is performed according to the

operand size. This is done to clarify the operation of the LSI. Refer to the relevant

assembler notation rules for the actual assembler descriptions.

@ (disp:4, Rn) ; Register indirect with displacement

@ (disp:8, GBR) ; GBR indirect with displacement

@ (disp:8, PC) ; PC-relative with displacement

disp:8, disp:12 ; PC-relative

Loading...

Loading...