UM0306 Controller area network (bxCAN)

305/519

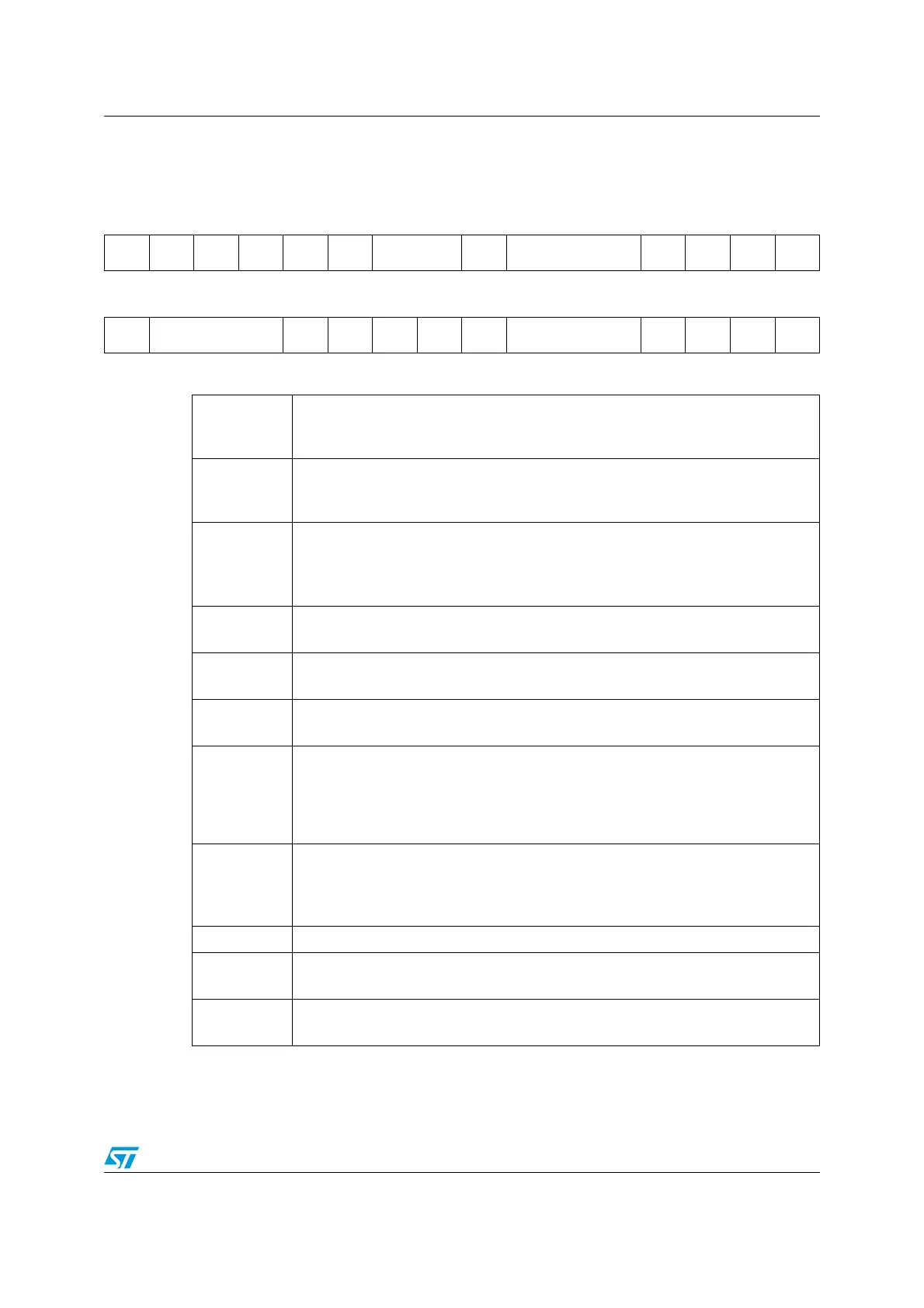

CAN transmit status register (CAN_TSR)

Address Offset: 08h

Reset value: 1C000000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LOW2 LOW1 LOW0 TME2 TME1 TME0 CODE[1:0]

ABRQ

2

Reserved

TERR

2

ALST2

TXOK

2

RQCP

2

rrrrrrrrrs rc_w1rc_w1rc_w1rc_w1

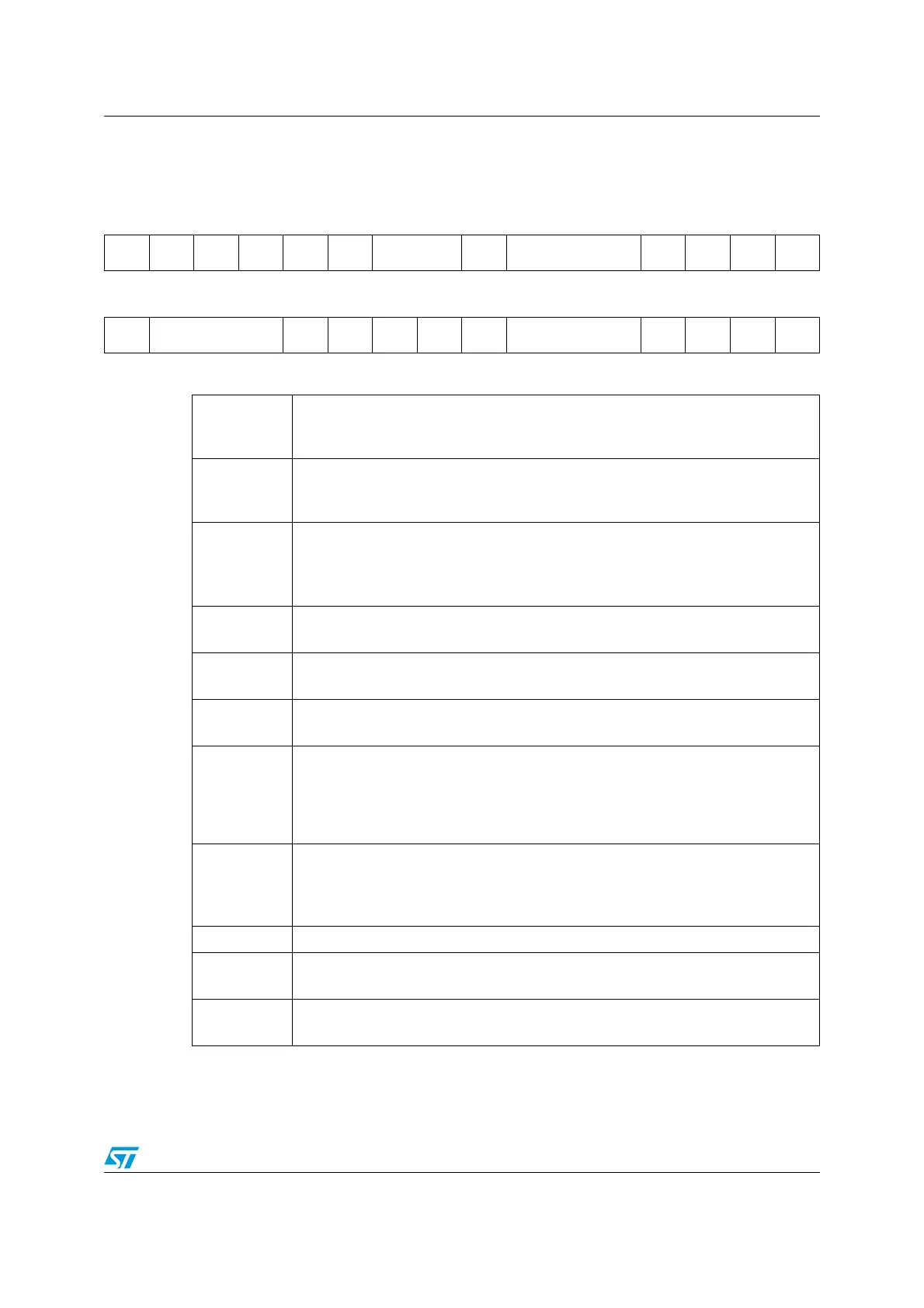

1514131211109876543210

ABRQ

1

Reserved

TERR

1

ALST1

TXOK

1

RQCP

1

ABRQ

0

Reserved

TERR

0

ALST0

TXOK

0

RQCP

0

rs rc_w1 rc_w1 rc_w1 rc_w1 rs rc_w1 rc_w1 rc_w1 rc_w1

Bit 31

LOW2: Lowest Priority Flag for Mailbox 2

This bit is set by hardware when more than one mailbox are pending for

transmission and mailbox 2 has the lowest priority.

Bit 30

LOW1: Lowest Priority Flag for Mailbox 1

This bit is set by hardware when more than one mailbox are pending for

transmission and mailbox 1 has the lowest priority.

Bit 29

LOW0: Lowest Priority Flag for Mailbox 0

This bit is set by hardware when more than one mailbox are pending for

transmission and mailbox 0 has the lowest priority.

Note: The LOW[2:0] bits are set to zero when only one mailbox is pending.

Bit 28

TME2: Transmit Mailbox 2 Empty

This bit is set by hardware when no transmit request is pending for mailbox 2.

Bit 27

TME1: Transmit Mailbox 1 Empty

This bit is set by hardware when no transmit request is pending for mailbox 1.

Bit 26

TME0: Transmit Mailbox 0 Empty

This bit is set by hardware when no transmit request is pending for mailbox 0.

Bits 25:24

CODE[1:0]: Mailbox Code

In case at least one transmit mailbox is free, the code value is equal to the number

of the next transmit mailbox free.

In case all transmit mailboxes are pending, the code value is equal to the number

of the transmit mailbox with the lowest priority.

Bit 23

ABRQ2: Abort Request for Mailbox 2

Set by software to abort the transmission request for the corresponding mailbox.

Cleared by hardware when the mailbox becomes empty.

Setting this bit has no effect when the mailbox is not pending for transmission.

Bits 22:20 Reserved, forced by hardware to 0.

Bit 19

TERR2: Transmission Error of Mailbox 2

This bit is set when the previous TX failed due to an error.

Bit 18

ALST2: Arbitration Lost for Mailbox 2

This bit is set when the previous TX failed due to an arbitration lost.

Loading...

Loading...