UM0306 Controller area network (bxCAN)

313/519

CAN bit timing register (CAN_BTR)

Address Offset: 1Ch

Reset value: 01230000h

Note: This register can only be accessed by the software when the CAN hardware is in

initialization mode.

14.8.2 Mailbox registers

This chapter describes the registers of the transmit and receive mailboxes. Refer to

Section 14.5.5: Message storage on page 295 for detailed register mapping.

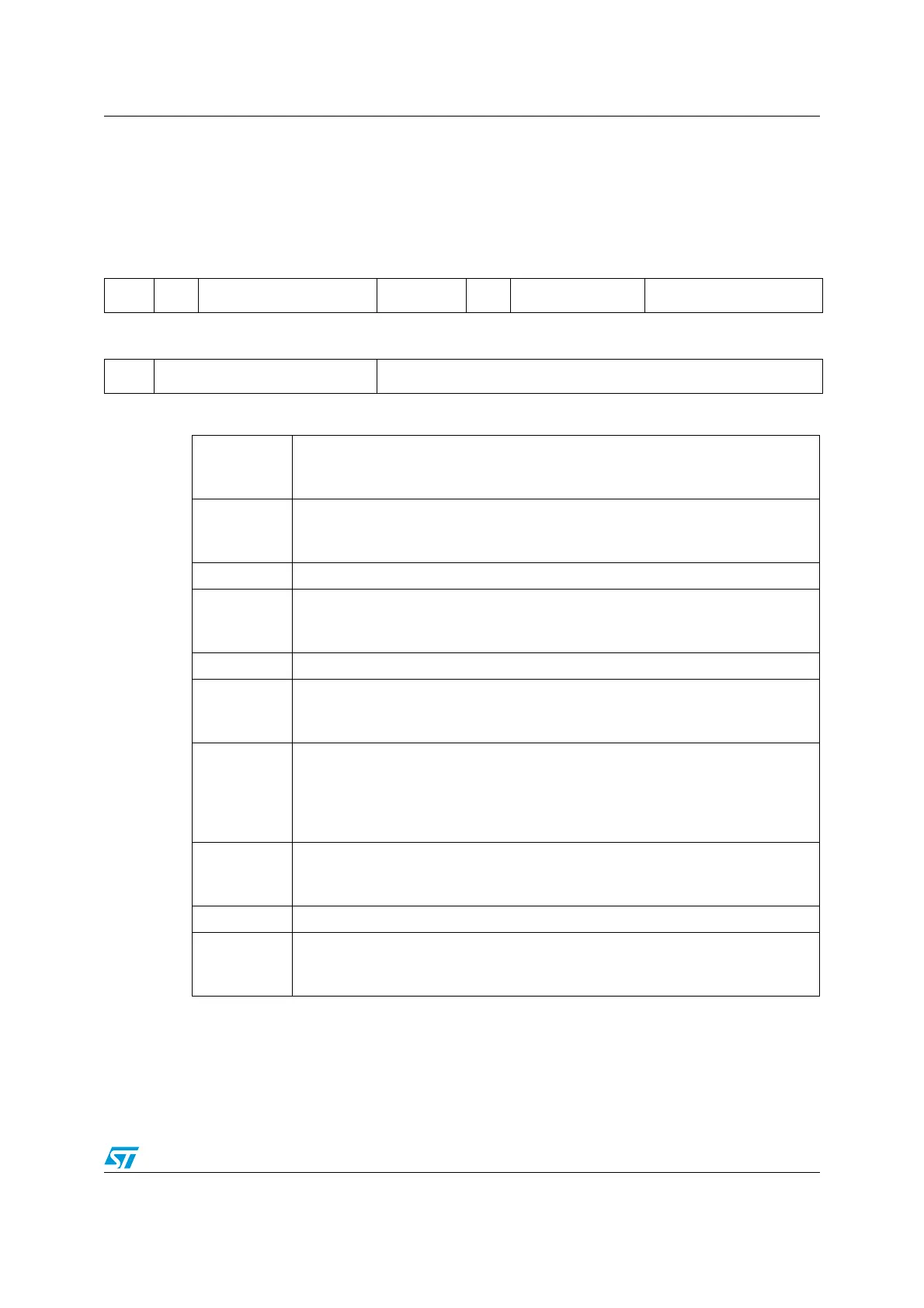

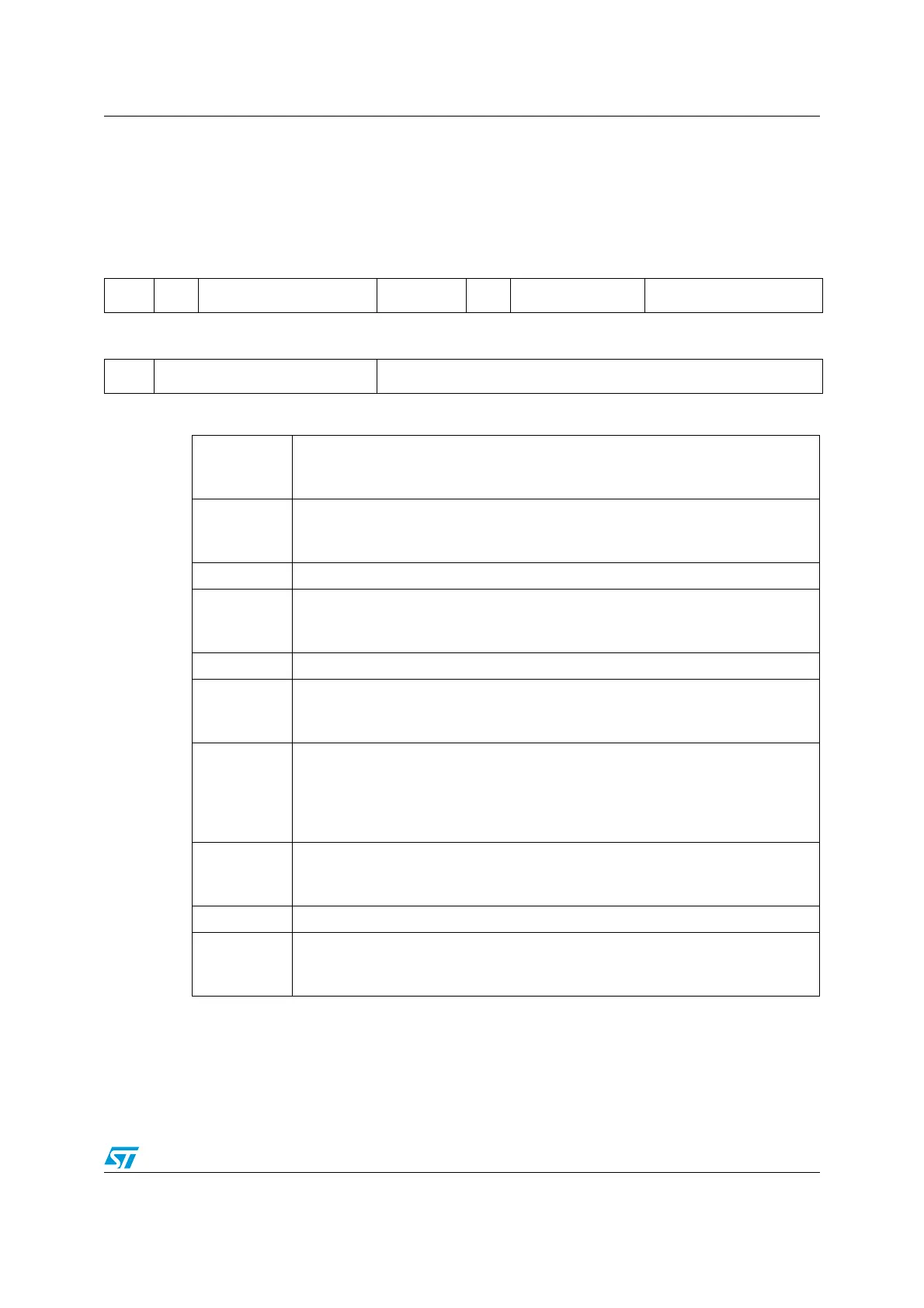

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SILM LBKM Reserved SJW[1:0] Res. TS2[2:0] TS1[3:0]

rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

Reserved Reserved BRP[9:0]

rw rw rw rw rw rw rw rw rw rw rw

Bit 31

SILM: Silent Mode (Debug)

0: Normal operation

1: Silent Mode

Bit 30

LBKM: Loop Back Mode (Debug)

0: Loop Back Mode disabled

1: Loop Back Mode enabled

Bits 29:26 Reserved, forced by hardware to 0.

Bits 25:24

SJW[1:0]: reSynchronization Jump Width

These bits define the maximum number of time quanta the CAN hardware is

allowed to lengthen or shorten a bit to perform the resynchronization.

Bit 23 Reserved, forced by hardware to 0.

Bits 22:20

TS2[2:0]: Time Segment 2

These bits define the number of time quanta in Time Segment 2.

t

BS2

= t

CAN

x (TS2[2:0] + 1)

Bits 19:16

TS1[3:0]: Time Segment 1

These bits define the number of time quanta in Time Segment 1

t

BS1

= t

CAN

x (TS1[3:0] + 1)

For more information on bit timing, please refer to Section 14.5.7: Bit timing on

page 296.

Bit 15

CLK8: CLK8 8MHz Clock Input

0: APB clock selected (fsys = PCLK1)

1: 8MHz XTAL clock selected (fsys = f

XTAL

)

Bits 14:10 Reserved, forced by hardware to 0.

Bits 9:0

BRP[9:0]: Baud Rate Prescaler

These bits define the length of a time quanta.

t

q

= (BRP[9:0]+1) x t

PCLK

Loading...

Loading...