UM0306 Controller area network (bxCAN)

323/519

Note: There are 14 filter banks, x=0..13. Each filter bank x is composed of two 32-bit registers,

CAN_FxR[1:0].

This register can only be modified when the FACTx bit of the CAN_FAxR register is cleared

or when the FINIT bit of the CAN_FMR register is set.

In all configurations:

Note: Depending on the scale and mode configuration of the filter the function of each register can

differ. For the filter mapping, functions description and mask registers association, refer to

Section 14.5.4: Identifier filtering on page 291.

A Mask/Identifier register in mask mode has the same bit mapping as in identifier list

mode.

For the register mapping/addresses of the filter banks please refer to the Table 44 on

page 324.

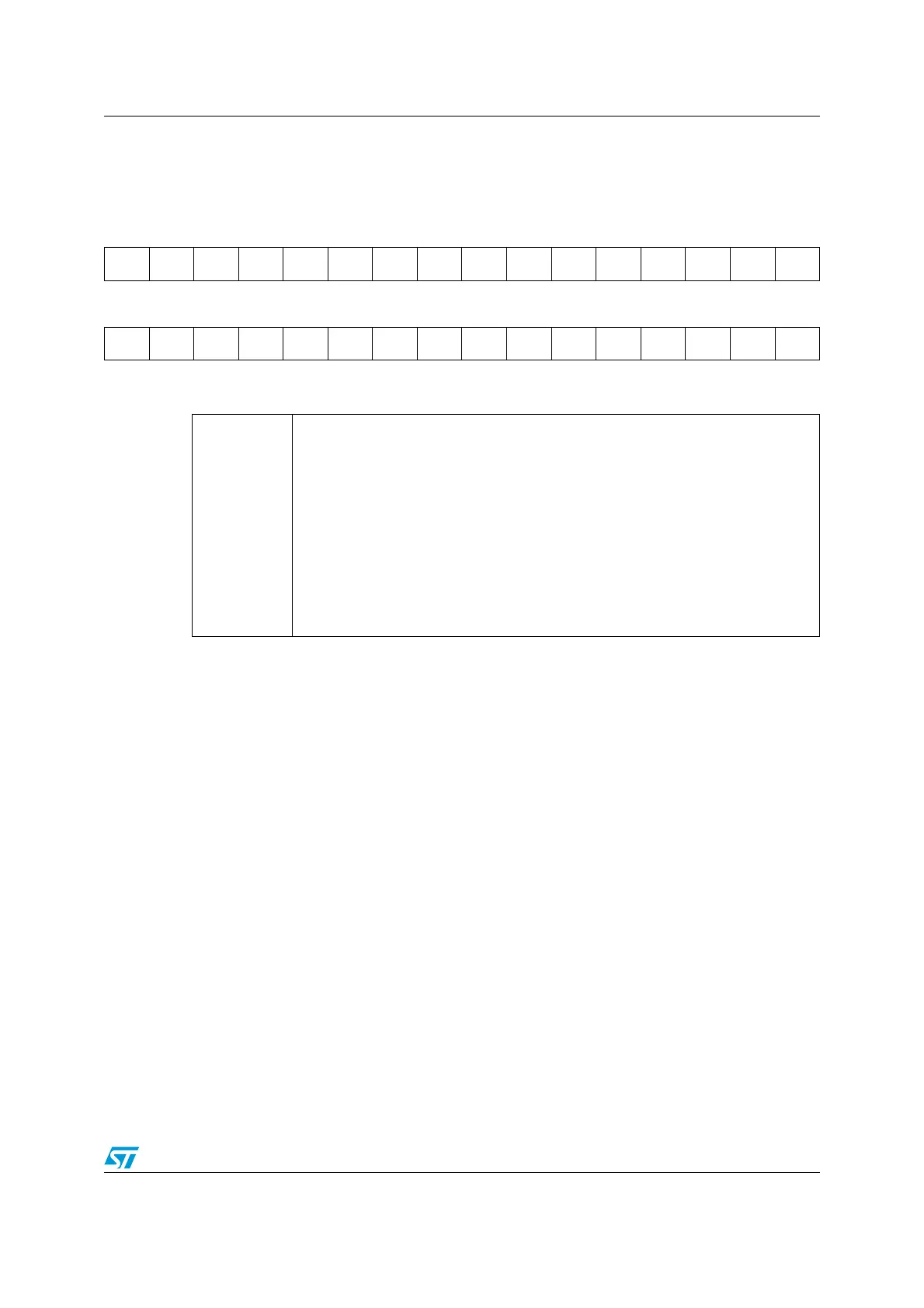

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

FB31 FB30 FB29 FB28 FB27 FB26 FB25 FB24 FB23 FB22 FB21 FB20 FB19 FB18 FB17 FB16

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

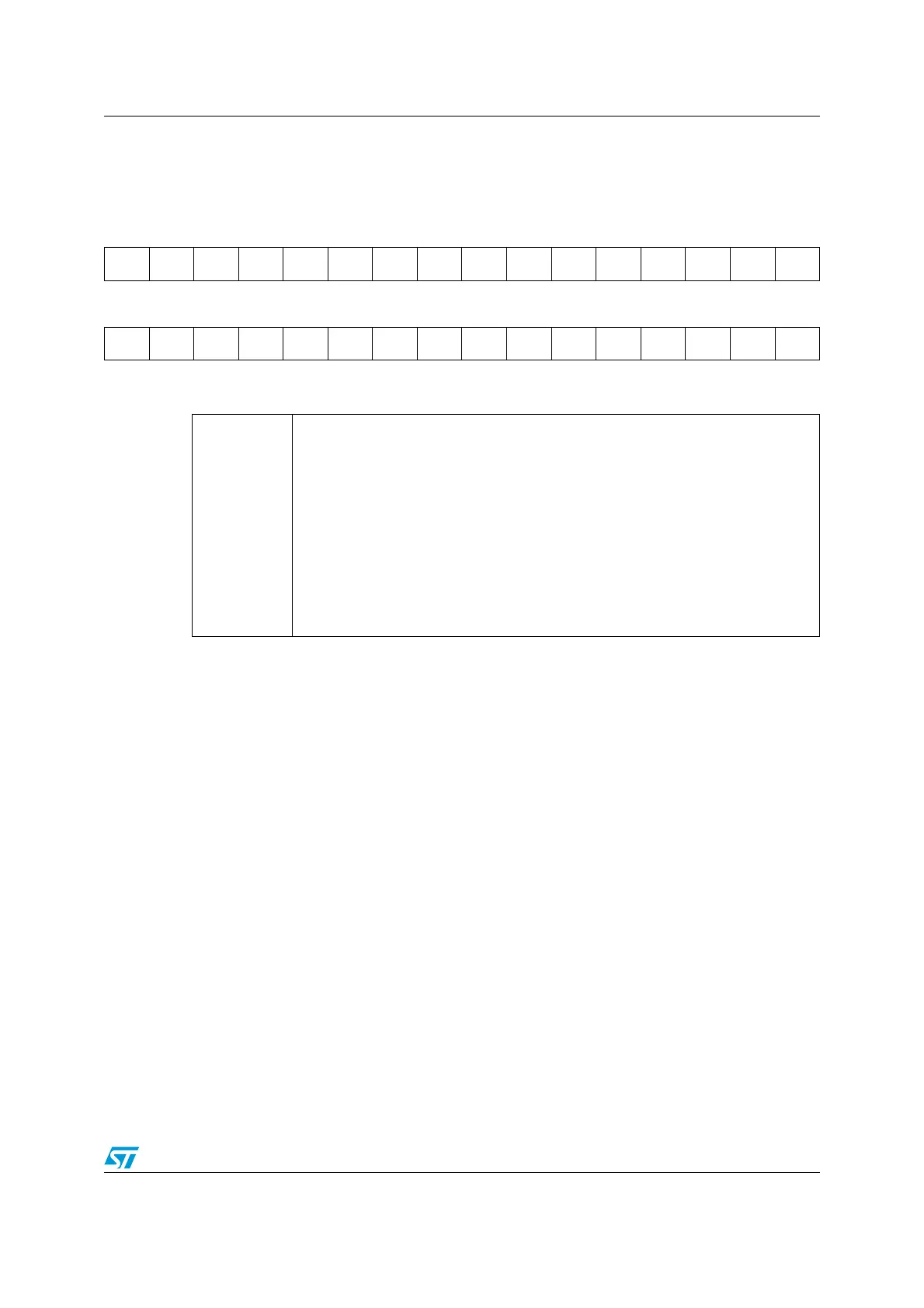

1514131211109876543210

FB15 FB14 FB13 FB12 FB11 FB10 FB9 FB8 FB7 FB6 FB5 FB4 FB3 FB2 FB1 FB0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0

FB[31:0] Filter Bits

Identifier

Each bit of the register specifies the level of the corresponding bit of the expected

identifier.

0: Dominant bit is expected

1: Recessive bit is expected

Mask

Each bit of the register specifies whether the bit of the associated identifier

register must match with the corresponding bit of the expected identifier or not.

0: Don’t care, the bit is not used for the comparison

1: Must match, the bit of the incoming identifier must have the same level has

specified in the corresponding identifier register of the filter.

Loading...

Loading...