Inter-integrated circuit (I2C) interface UM0306

350/519

15.6.5 Data register (I2C_DR)

Address offset: 10h

Reset Value: 0000h

Bits 7:1

ADD2[7:1]: Interface address

bits 7:1 of address in dual addressing mode

Bit 0

ENDUAL: Dual addressing mode enable

0: Only OAR1 is recognized in 7-bit addressing mode

1: Both OAR1 and OAR2 are recognized in 7-bit addressing mode

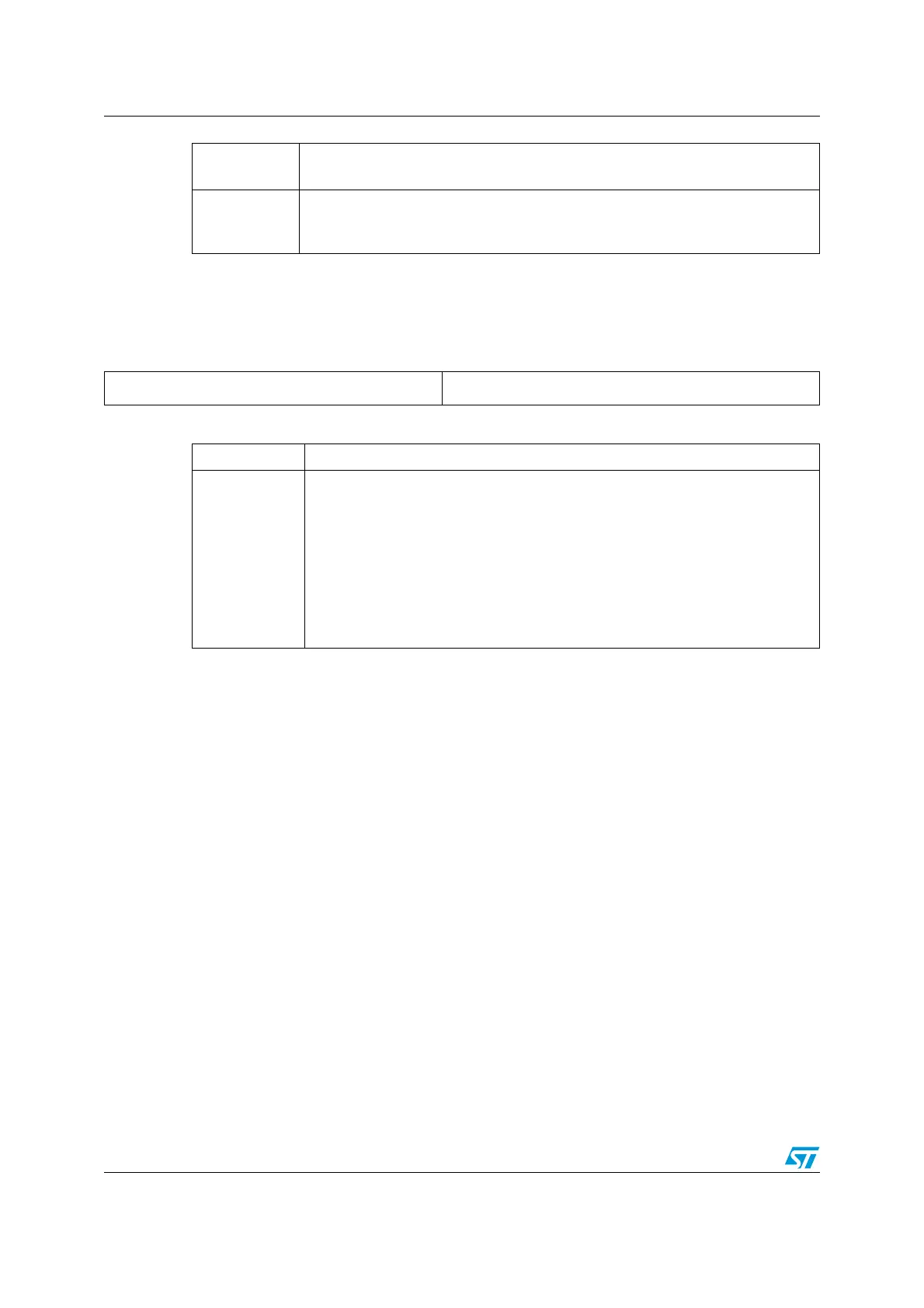

151413121110987 654321 0

Reserved DR[7:0]

rw rw rw rw rw rw rw rw

Bits 15:8 Reserved, forced by hardware to 0.

Bits 7:0

DR[7:0] 8-bit Data Register

(1)(2)(3)

Byte received or to be transmitted to the bus.

– Transmitter mode: Byte transmission starts automatically when a byte is

written in the DR register. A continuous transmit stream can be maintained if

the next data to be transmitted is put in DR once the transmission is started

(TxE=1)

– Receiver mode: Received byte is copied into DR (RxNE=1). The received data

in the DR register must be read before the next data reception, otherwise an

overrun occurs and the last byte will be lost.

1. In slave mode, the address is not copied into DR.

2. Write collision is not managed (DR can be written if TxE=0).

3. If an ARLO event occurs on ACK pulse, the received byte is not copied into DR and so cannot be read.

Loading...

Loading...