Analog/digital converter (ADC) UM0306

478/519

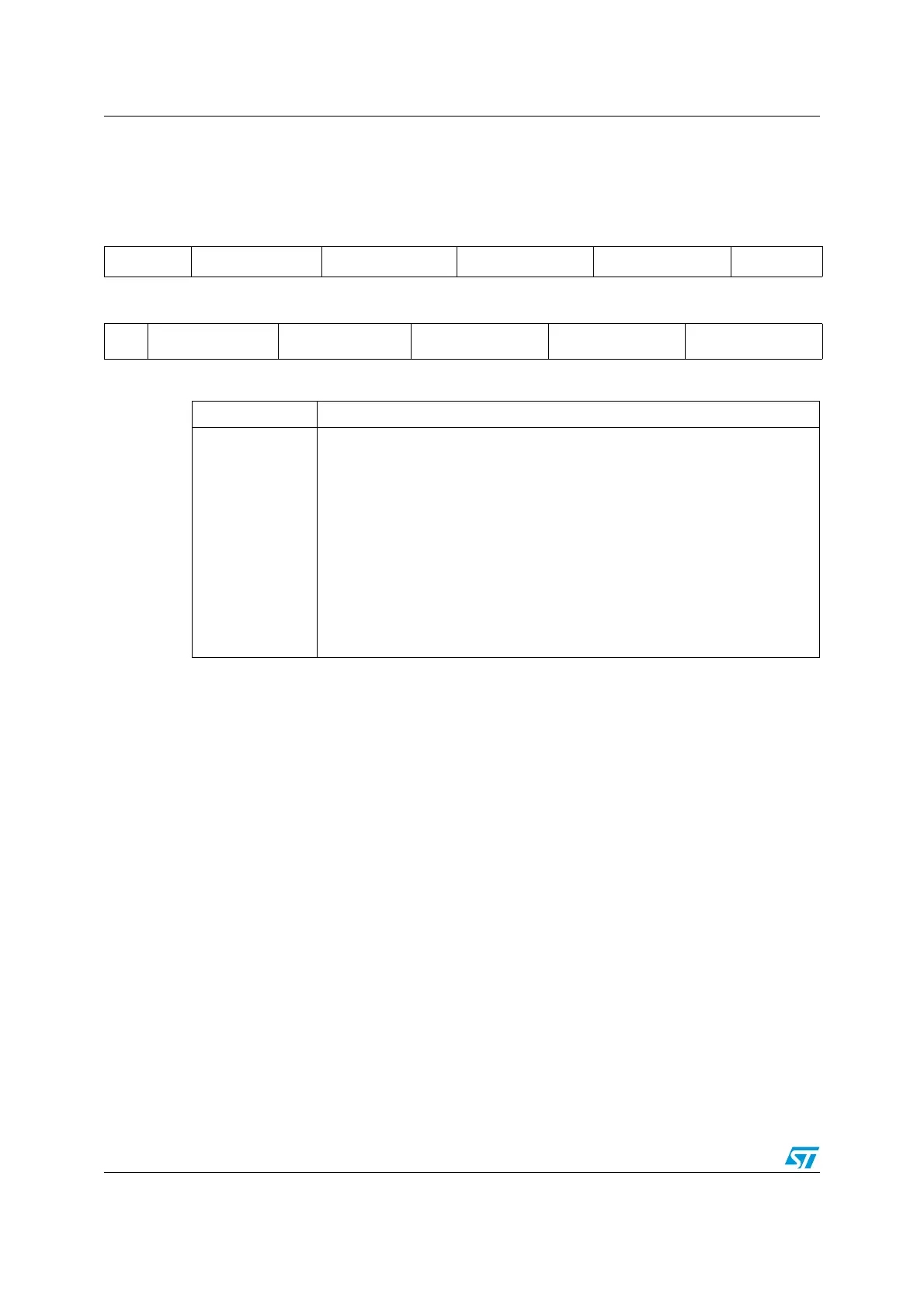

19.13.5 ADC sample time register 2 (ADC_SMPR2)

Address offset: 10h

Reset value: 0000 0000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved SMP9[2:0] SMP8[2:0] SMP7[2:0] SMP6[2:0] SMP5[2:1]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

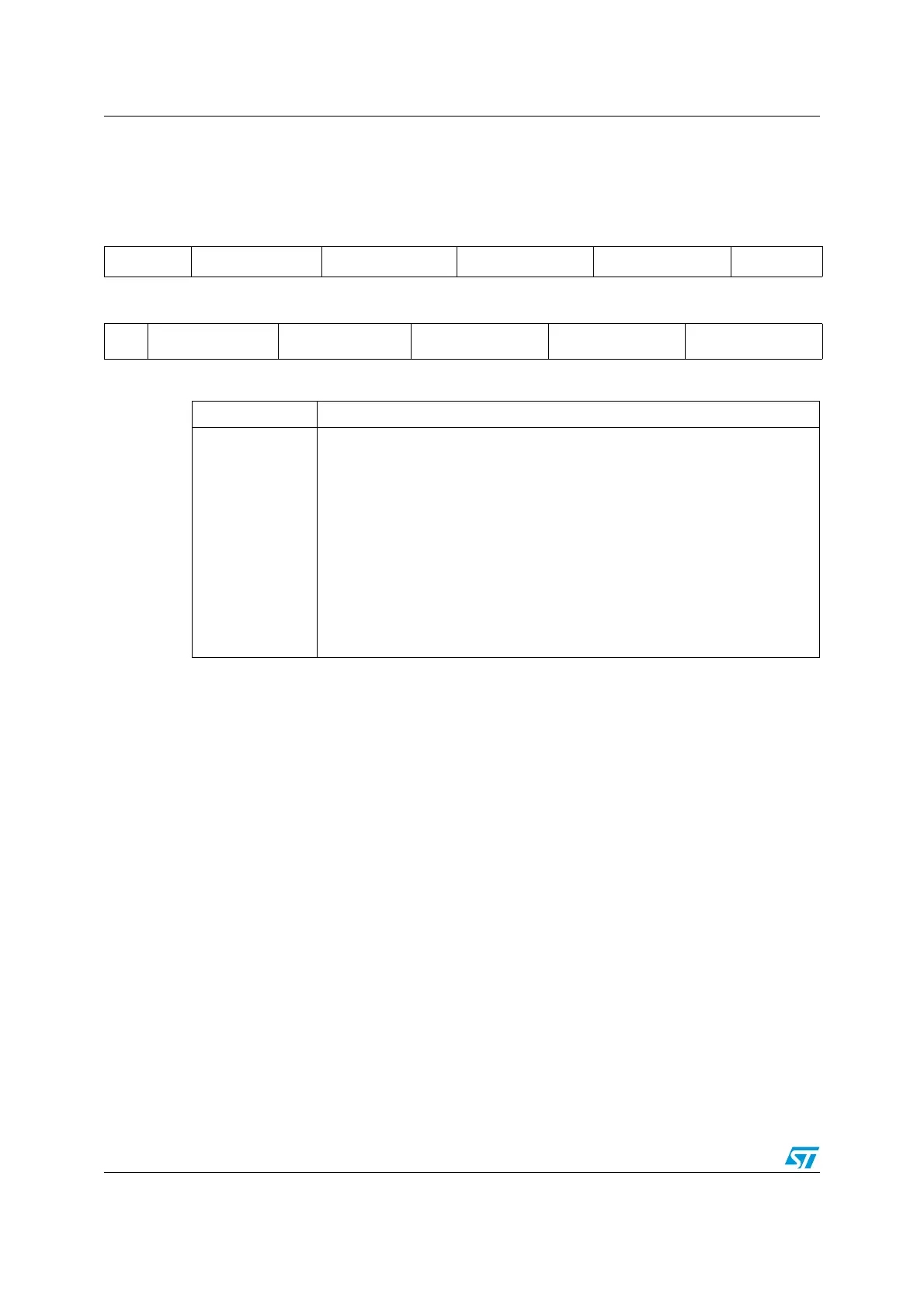

1514131211109876543210

SMP

5_0

SMP4[2:0] SMP3[2:0] SMP2[2:0] SMP1[2:0] SMP0[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:30 Reserved, must be kept cleared.

Bits 29:0

SMPx[2:0]: Channel x Sample time selection

These bits are written by software to select the sample time individually for

each channel. During sample cycles channel selection bits must remain

unchanged.

000: 1.5 cycles

001: 7.5 cycles

010: 13.5 cycles

011: 28.5 cycles

100: 41.5 cycles

101: 55.5 cycles

110: 71.5 cycles

111: 239.5 cycles

Loading...

Loading...