AMCC Proprietary 103

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

Zone protection can alter write protection (see “Zone Protection” on page 103). In addition, only zone protection

can prevent read access of a page defined by a TLB entry.

5.7.1.4 Zone Protection

Each TLB entry contains a 4-bit zone select (ZSEL) field. A zone is an arbitrary identifier for grouping TLB entries

(memory pages) for purposes of protection. As many as 16 different zones may be defined. Any zone can have

any number of member pages.

Each zone is associated with a 2-bit field (Z0-Z15) in the ZPR. The values of the field define how protection is

applied to all pages that are member of that zone. Changing the value of the ZPR field can alter the protection

attributes of all pages in the zone. Without ZPR, the change would require finding, reading, altering, and rewriting

the TLB entry for each page in a zone, individually. The ZPR provides a much faster means of altering the

protection for groups of memory pages.

The ZSEL values 0-15 select ZPR fields Z0-Z15, respectively.

The fields are defined within the ZPR as follows:

While it is common for TLB_entry[EX, WR] to be identical for all member pages in a group, this is not required. The

ZPR field alters the protection defined by TLB_entry[EX] and TLB_entry[WR], on a page-by-page basis, as shown

in the ZPR illustration. An application program (presumed to be running in the problem state) can have execute

and write permissions as defined by TLB_entry[EX] and TLB_entry[WR] for the individual pages, or no access

(denies loads, as well as stores and execution), or complete access. Figure 5-5 shows the Zone Protection

Register.

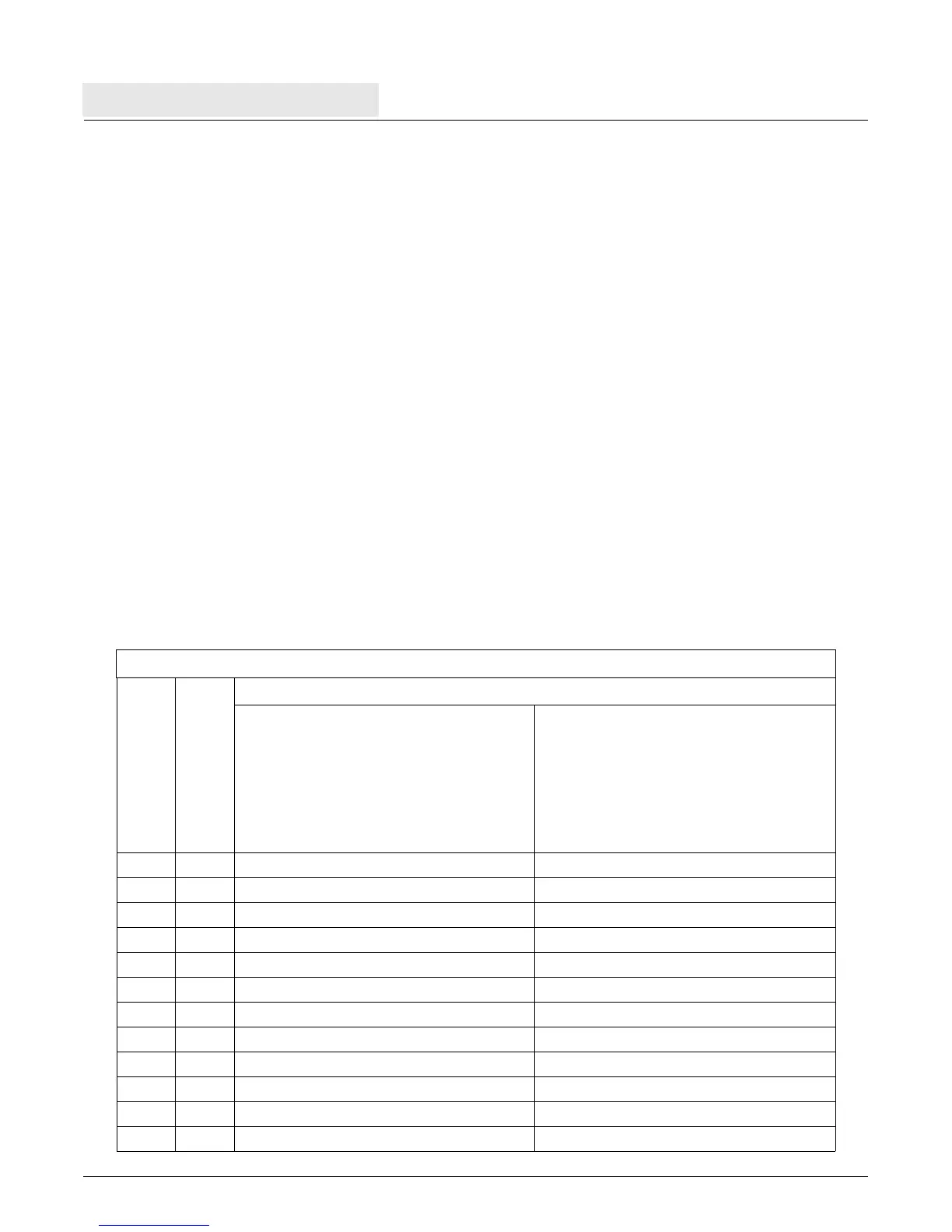

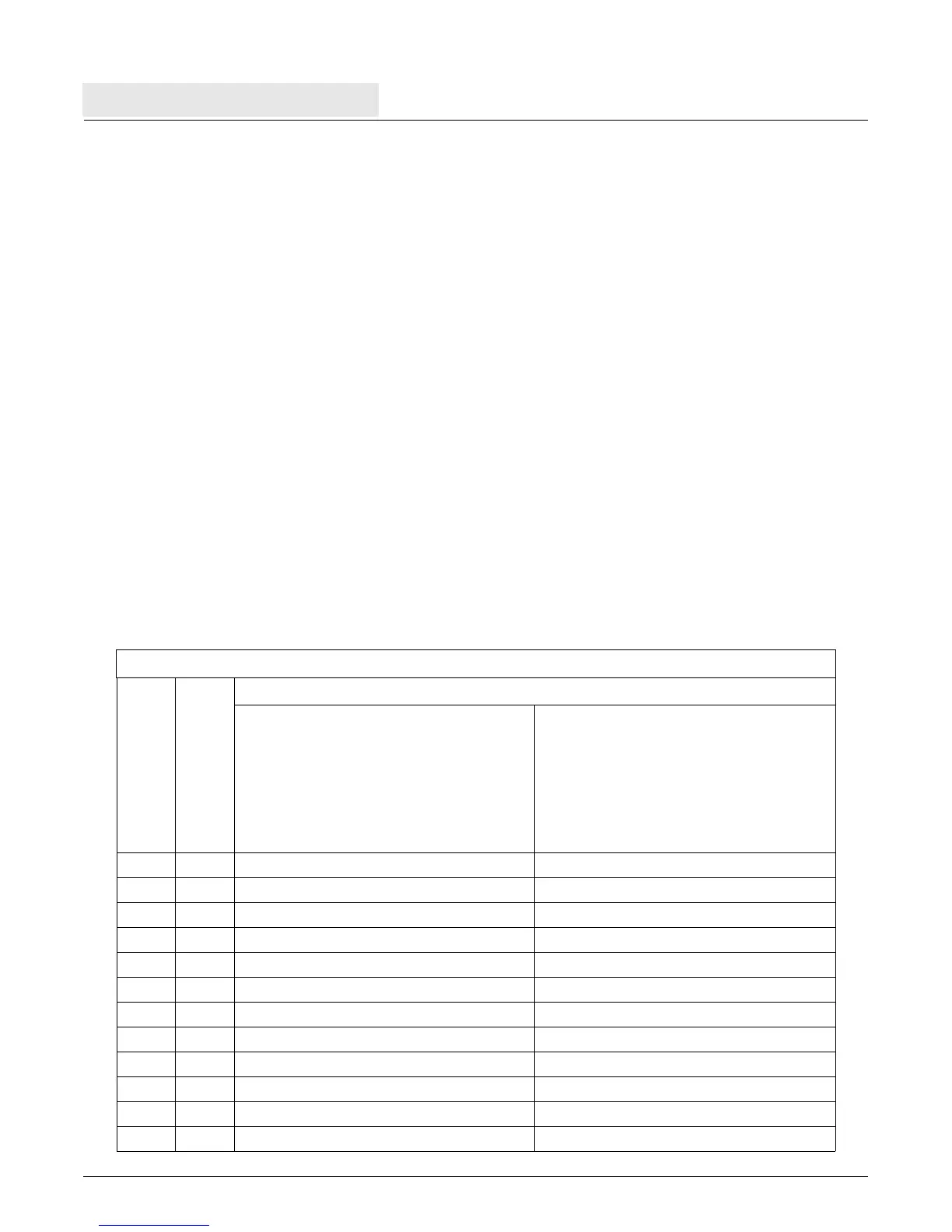

Figure 5-5. Zone Protection Register (ZPR)

0:1 Z0

TLB page access control for all pages in this zone.

In the problem state (MSR[PR] = 1):

00 No access

01 Access controlled by applicable TLB_entry[EX,

WR]

10 Access controlled by applicable TLB_entry[EX,

WR]

11 Accessed as if execute and write permissions

(TLB_entry[EX, WR]) are granted

In the supervisor state (MSR[PR] = 0):

00 Access controlled by applicable TLB_entry[EX,

WR]

01 Access controlled by applicable TLB_entry[EX,

WR]

10 Accessed as if execute and write permissions

(TLB_entry[EX, WR]) are granted

11 Accessed as if execute and write permissions

(TLB_entry[EX, WR]) are granted

2:3 Z1 See the description of Z0.

4:5 Z2 See the description of Z0.

6:7 Z3 See the description of Z0.

8:9 Z4 See the description of Z0.

10:11 Z5 See the description of Z0.

12:13 Z6 See the description of Z0.

14:15 Z7 See the description of Z0.

16:17 Z8 See the description of Z0.

18:19 Z9 See the description of Z0.

20:21 Z10 See the description of Z0.

22:23 Z11 See the description of Z0.

24:25 Z12 See the description of Z0.

Loading...

Loading...