154 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

The settings of DBCR1[DV1M] and DBCR1[DV2M] are more precisely defined in Table 8-6 on page 155 and

Table 8-7 on page 155. (

n enables the table to apply to DBCR1[DV1M, DV2M] and DBCR1[DV1BE, DV2BE]).

DV

nBE

m

indicates bytes selected (or not selected) for comparison in DBCR1[DVnBE].

When DBCR1[DV

nM] = 01, the comparison is an AND; all bytes must compare to the appropriate bytes of DVC1.

When DBCR1[DV

nM] = 10, the comparison is an OR; at least one of the selected bytes must compare to the

appropriate bytes of DVC1.

When DBCR1[DV

nM] = 11, the comparison is an AND-OR (halfword) comparison. This is intended for use when

DBCR1[DV

nBE] is set to 0011, 0111, or 1111. Other values of DBCR1[DVnBE] can be compared, but the results

are more easily understood using the AND and OR comparisons. In Table 8-5, “not” is ¬, AND is ∧, and OR is ∨.

Table 8-6 illustrates comparisons for aligned DVC accesses, that is, words, halfwords, or bytes on naturally aligned

boundaries (all byte accesses are aligned).

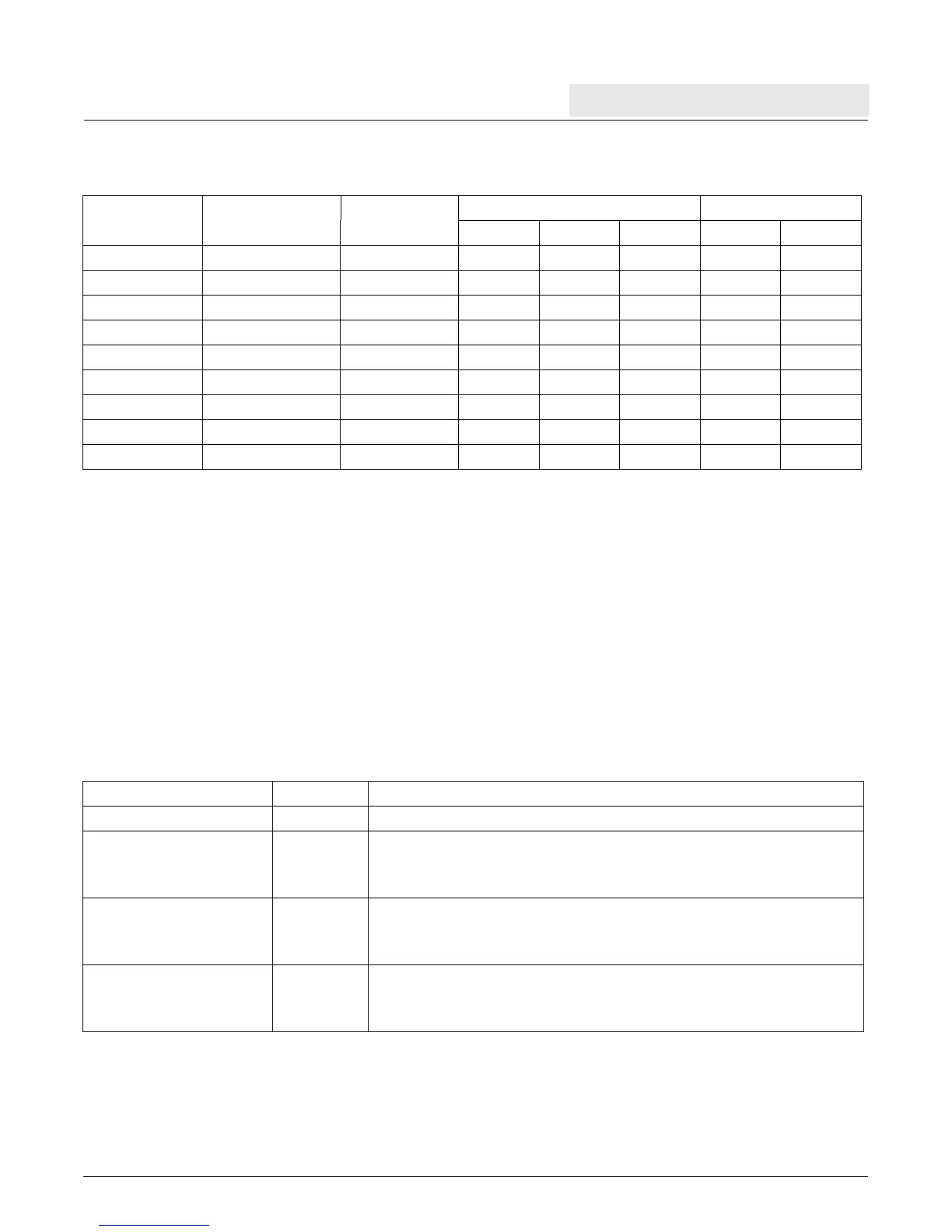

Table 8-4. Setting of DBSR Bits for DAC and DVC Events

DBCR1 DBSR

DACn Event DVCn Enabled DVCn Event [DnR] [DnW] [DA12] [DRn] [DWn]

0 — — — — — Hold Hold

— — — 0 0 — Hold Hold

10—01—HoldWA

1 0 — 1 0 — RA Hold

10—11—RAWA

1 1 0 — — — Hold Hold

11101—HoldWV

1 1 1 1 0 — RV Hold

11111—RVWV

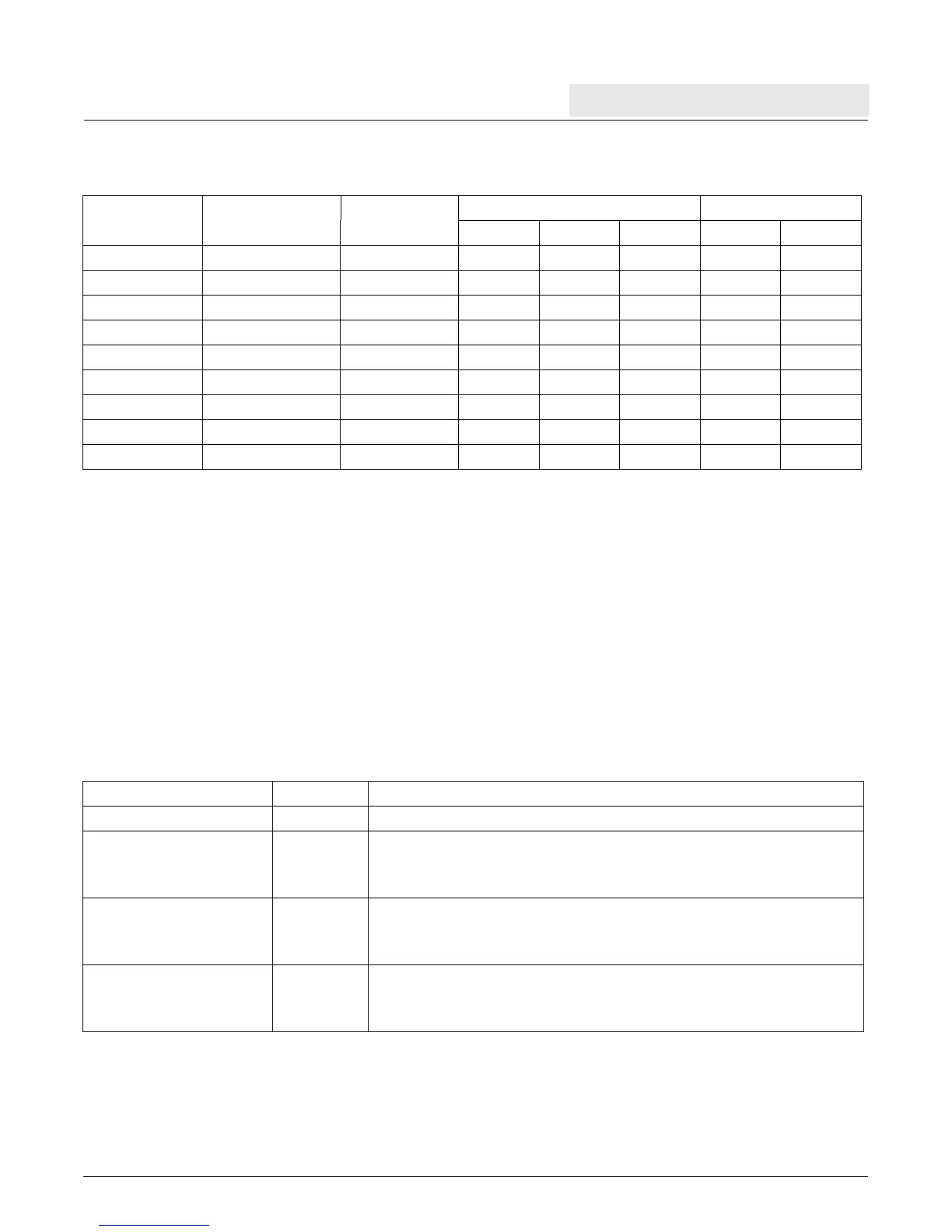

Table 8-5. Comparisons Based on DBCR1[DVnM]

DBCR1[DVnM] Setting Operation Comparison

00 — Undefined

01 AND

(

¬DVnBE

0

∨ (DVC1[byte 0] = data[byte 0])) ∧

(¬DVnBE

1

∨ (DVC1[byte 1] = data[byte 1])) ∧

(¬DVnBE

2

∨ (DVC1[byte 2] = data[byte 2])) ∧

(¬DVnBE

3

∨ (DVC1[byte 3] = data[byte 3]))

10 OR

(DV

nBE

0

∧ (DVC1[byte 0] = data[byte 0])) ∨

(DVnBE

1

∧ (DVC1[byte 1] = data[byte 1])) ∨

(DVnBE

2

∧ (DVC1[byte 2] = data[byte 2])) ∨

(DVnBE

3

∧ (DVC1[byte 3] = data[byte 3]))

11 AND-OR

(DV

nBE

0

∧ (DVC1[byte 0] = data[byte 0])) ∧

(DVnBE

1

∧ (DVC1[byte 1] = data[byte 1])) ∨

(DVnBE

2

∧ (DVC1[byte 2] = data[byte 2])) ∧

(DVnBE

3

∧ (DVC1[byte 3] = data[byte 1]))

Loading...

Loading...