AMCC Proprietary 262

Revision 1.02 - September 10, 2007

PPC405 Processor

mcrxr

Move to Condition Register from XER

Preliminary User’s Manual

25.Instruction Setmcrxr

Move to Condition Register from XER

n ← BF

(CR[CRn])

← XER

0:3

XER

0:3

←

4

0

The contents of XER

0:3

are placed into the CR field specified by the BF field. XER

0:3

are then set to 0.

This transfer is positional, by bit number, so the mnemonics associated with each bit are changed. See Table 9-18

for clarification.

If instruction bit 31 contains 1, the contents of CR[CR0] are undefined.

Registers Altered

• CR[CRn] where n is specified by the BF field.

• XER[SO, OV, CA]

Invalid Instruction Forms

• Reserved fields

Architecture Note

This instruction is part of the PowerPC User Instruction Set Architecture.

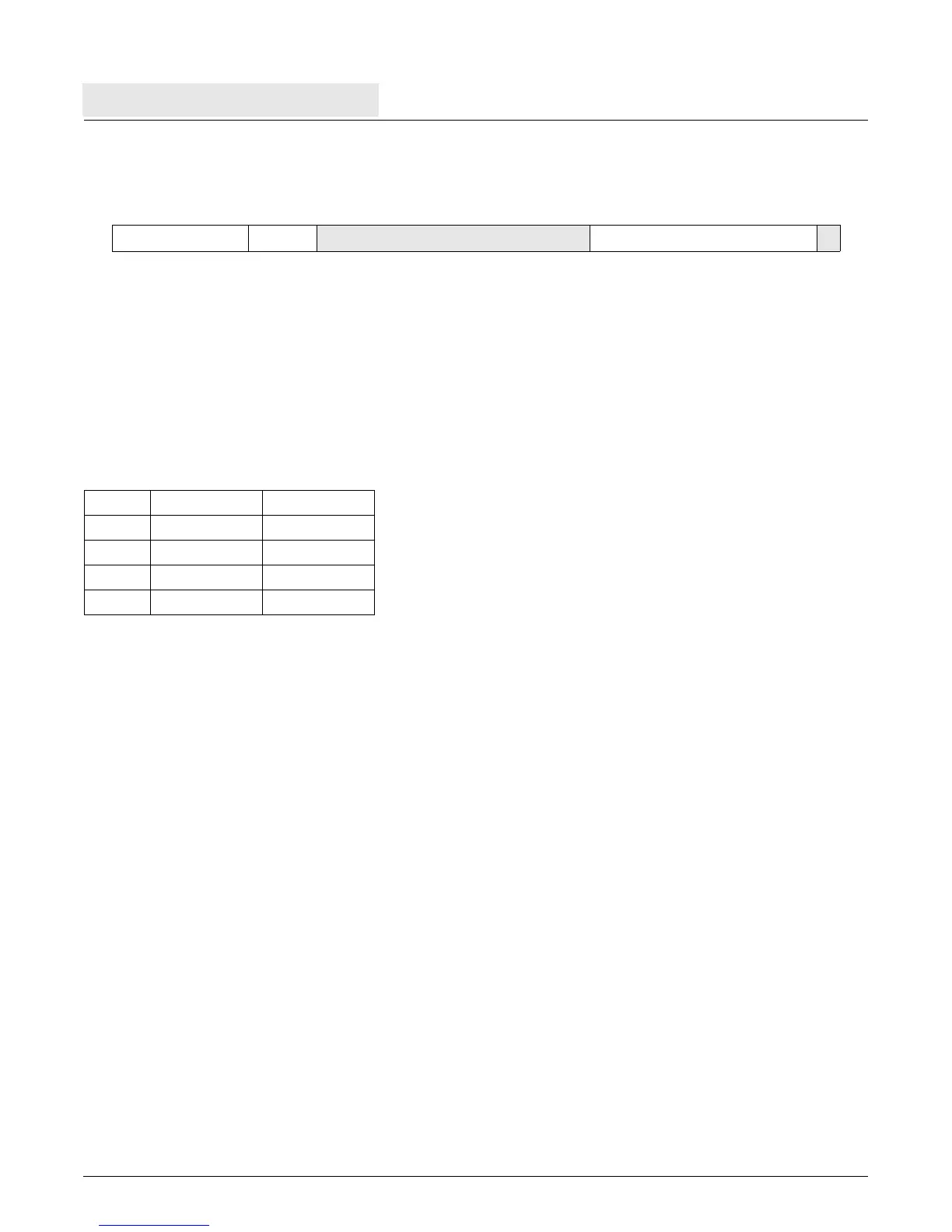

mcrxr BF

31 BF

512

069 21 31

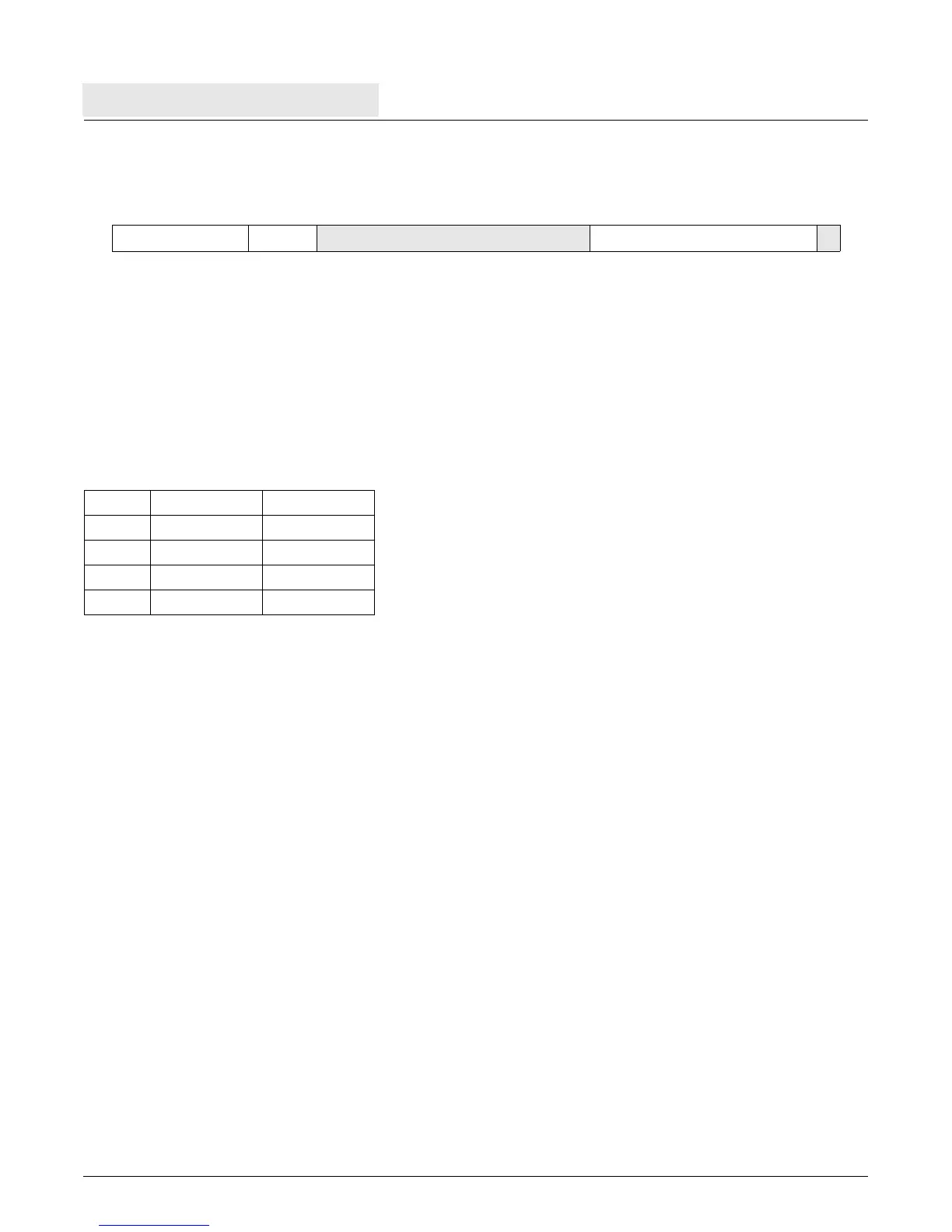

Table 9-18. Transfer Bit Mnemonic Assignment

Bit XER Usage CR Usage

0SO LT

1OV GT

2CA EQ

3ReservedSO

Loading...

Loading...