AMCC Proprietary 184

Revision 1.02 - September 10, 2007

PPC405 Processor

bclr

Branch Conditional to Link Register

Preliminary User’s Manual

bclr

Branch Conditional to Link Register

if BO

2

= 0 then

CTR

← CTR – 1

if (BO

2

= 1 ∨ ((CTR = 0) = BO

3

)) ∧ (BO

0

=1∨ (CR

BI

=BO

1

)) then

NIA

← LR

0:29

||

2

0

else

NIA

← CIA + 4

if LK = 1 then

(LR)

← CIA + 4

PC

← NIA

If bit 2 of the BO field contains 0, the CTR is decremented.

The BI field specifies a bit in the CR to be used as the condition of the branch.

The next instruction address (NIA) is the target address of the branch. The NIA is formed by concatenating the 30

most significant bits of the LR with two 0-bits on the right.

The BO field controls options that determine when program flow is transferred to the NIA. The BO field also

controls branch prediction, a performance-improvement feature. See Branch Prediction on page 52 for a complete

discussion.

If the LK field contains 1, then (CIA + 4) is placed into the LR.

Registers Altered

•CTR if BO

2

contains 0

• LR if LK contains 1

Invalid Instruction Forms

• Reserved fields

Architecture Note

This instruction is part of the PowerPC User Instruction Set Architecture.

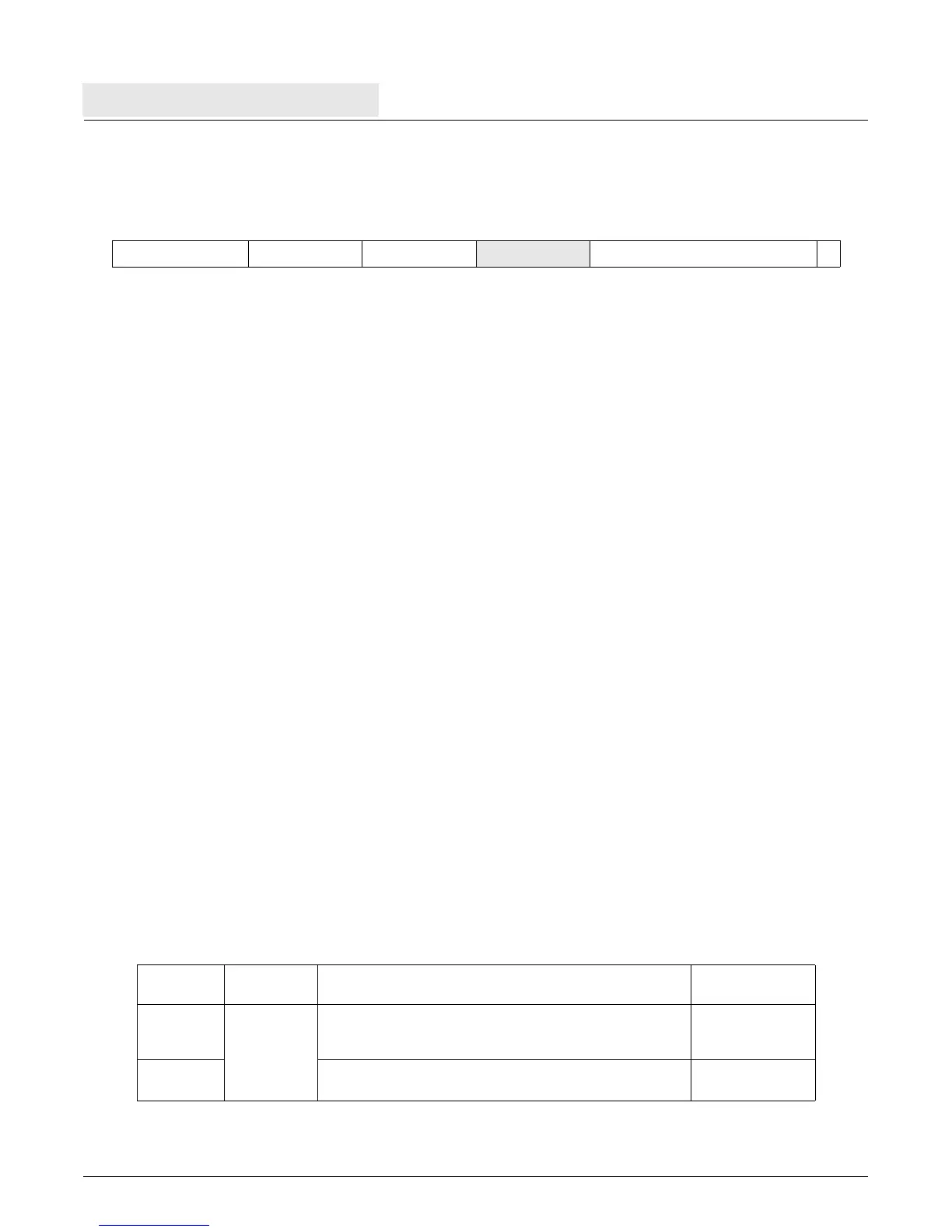

bclr BO, BI LK = 0

bclrl BO, BI LK =1

19 BO BI

16 LK

0 6 11 16 21 31

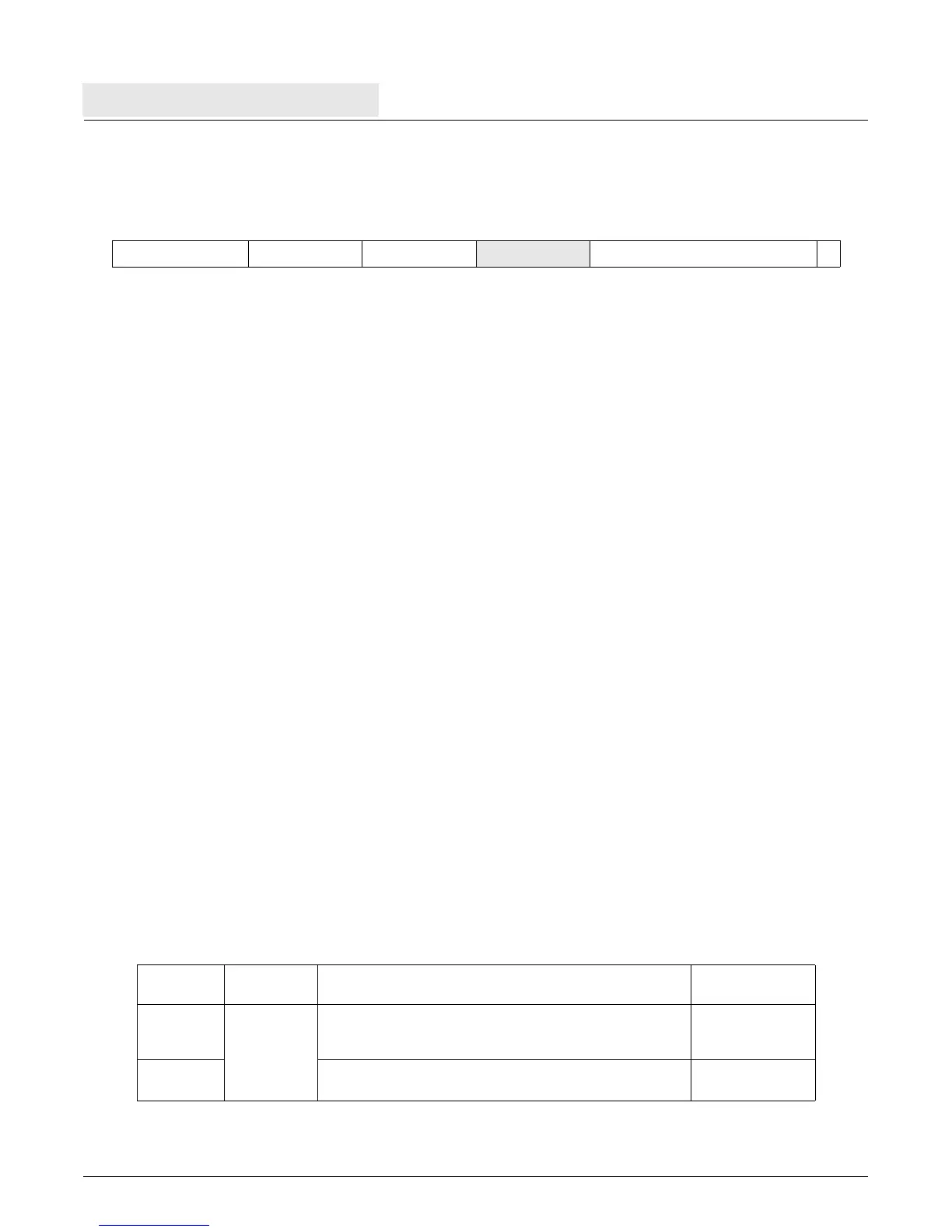

Table 9-9. Extended Mnemonics for bclr, bclrl

Mnemonic Operands Function

Other Registers

Altered

blr

Branch unconditionally to address in LR.

Extended mnemonic for

bclr 20,0

blrl

Extended mnemonic for

bclrl 20,0

(LR)

← CIA + 4.

Loading...

Loading...