400 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

B.3 Privileged Instructions

Table B-4 lists instructions that are under control of the MSR[PR] bit. These instructions are not allowed to be

executed when MSR[PR] = 1:

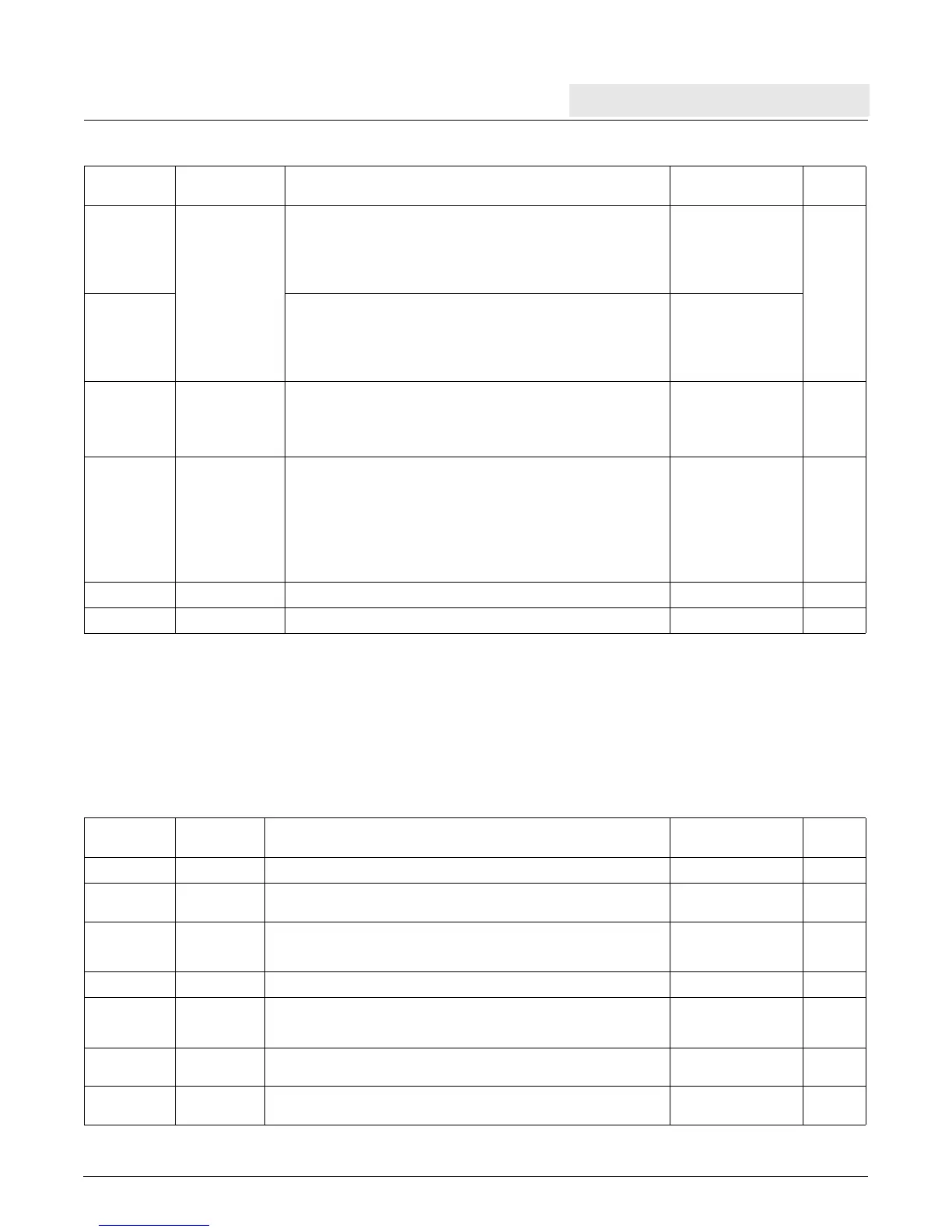

tlbsx RT,RA,RB Search the TLB array for a valid entry which translates the EA

EA = (RA|0) + (RB).

If found,

(RT)

← Index of TLB entry.

If not found,

(RT) Undefined.

337

tlbsx. If found,

(RT) ← Index of TLB entry.

CR[CR0]

EQ

← 1.

If not found,

(RT) Undefined.

CR[CR0]

EQ

← 1.

CR[CR0]

LT,GT,SO

tlbsync tlbsync does not complete until all previous TLB-update

instructions executed by this processor have been received and

completed by all other processors.

For the PPC405, tlbsync is a no-op.

338

tlbwe RS, RA,WS If WS = 0:

Write TLBHI portion of the selected TLB entry from RS.

Write the TID field of the selected TLB entry from the PID register.

TLBHI[(RA)]

← (RS)

TLB[(RA)]

TID

← (PID)

24:31

If WS = 1:

Write TLBLO portion of the selected TLB entry from RS.

TLBLO[(RA)]

← (RS)

339

wrtee RS Write value of RS

16

to MSR[EE]. 347

wrteei E Write value of E to MSR[EE]. 348

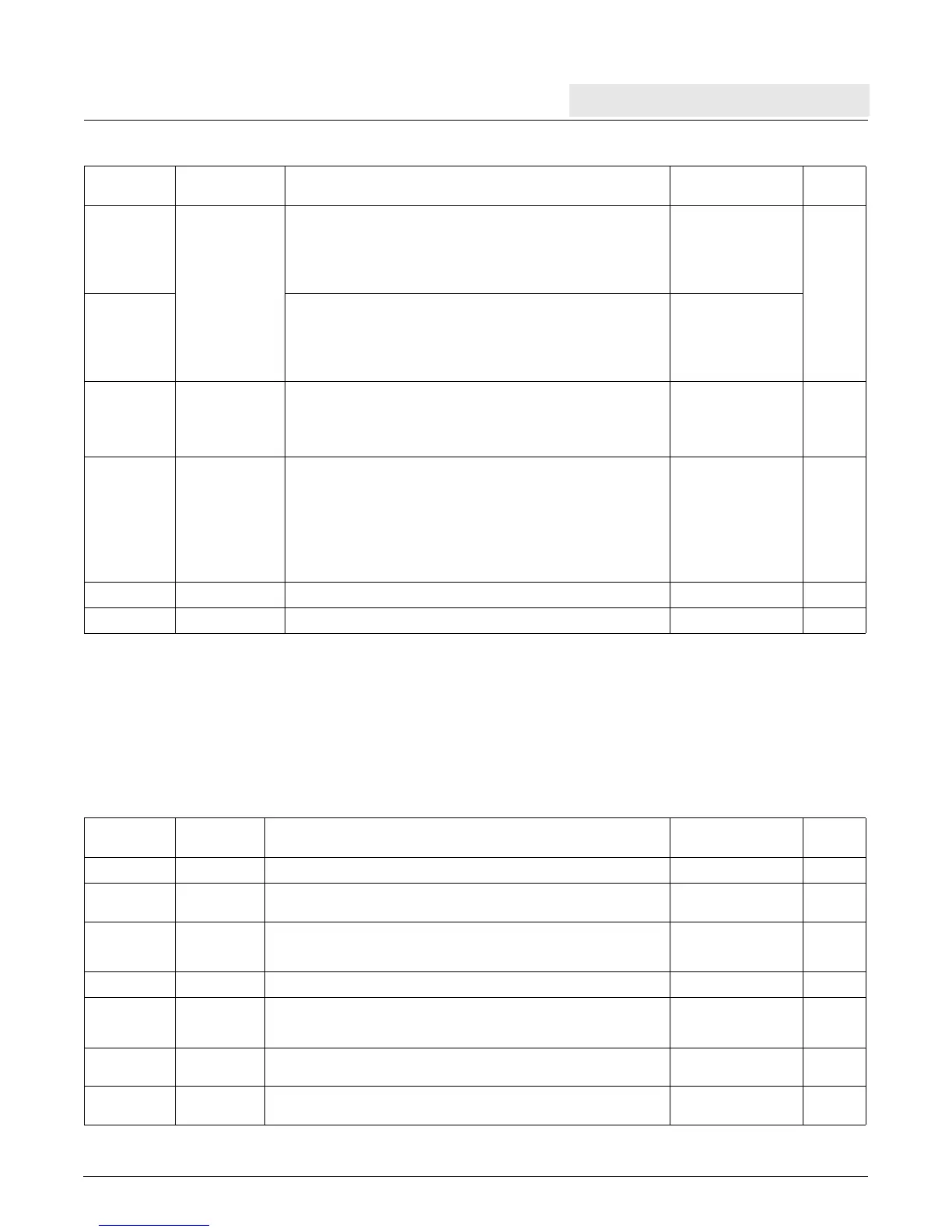

Table B-4. Privileged Instructions

Mnemonic Operands Function

Other Registers

Changed

Page

dcbi RA, RB Invalidate the data cache block which contains the EA (RA|0) + (RB). 204

dccci RA, RB Invalidate the data cache congruence class associated with the EA

(RA|0) + (RB).

210

dcread RT, RA, RB Read either tag or data information from the data cache congruence

class associated with the EA (RA|0) + (RB).

Place the results in RT.

211

iccci RA, RB Invalidate instruction cache. 221

icread RA, RB Read either tag or data information from the instruction cache

congruence class associated with the EA (RA|0) + (RB).

Place the results in ICDBDR.

221

mfdcr RT, DCRN Move from DCR to RT,

(RT)

← (DCR(DCRN)).

264

mfmsr RT Move from MSR to RT,

(RT)

← (MSR).

265

Table B-3. Instructions in the IBM PowerPC Embedded Environment (Continued)

Mnemonic Operands Function

Other Registers

Changed

Page

Loading...

Loading...