AMCC Proprietary 191

Revision 1.02 - September 10, 2007

PPC405 Processor

cmpli

Compare Logical Immediate

Preliminary User’s Manual

cmpli

Compare Logical Immediate

c

0:3

←

4

0

if (RA) (

16

0 || IM) then c

0

← 1

if (RA) (

16

0 || IM) then c

1

← 1

if (RA) (

16

0 || IM) then c

2

← 1

c

3

← XER[SO]

n

← BF

CR[CRn] ← c

0:3

The IM field is extended to 32 bits by concatenating 16 0-bits to its left. The contents of register RA are compared

with IM using a 32-bit unsigned compare.

The CR field specified by the BF field is updated to reflect the results of the compare and the value of XER[SO] is

placed into the same CR field.

Registers Altered

• CR[CRn] where n is specified by the BF field

Invalid Instruction Forms

• Reserved fields

Programming Note

The PowerPC Architecture defines this instruction as cmpli BF,L,RA,IM, where L selects operand size for 64-bit

PowerPC implementations. For all 32-bit PowerPC implementations, L = 0 is required (L = 1 is an invalid form);

hence for the PPC405, use of the extended mnemonic cmplwi BF,RA,IM is recommended.

Architecture Note

This instruction is part of the PowerPC User Instruction Set Architecture.

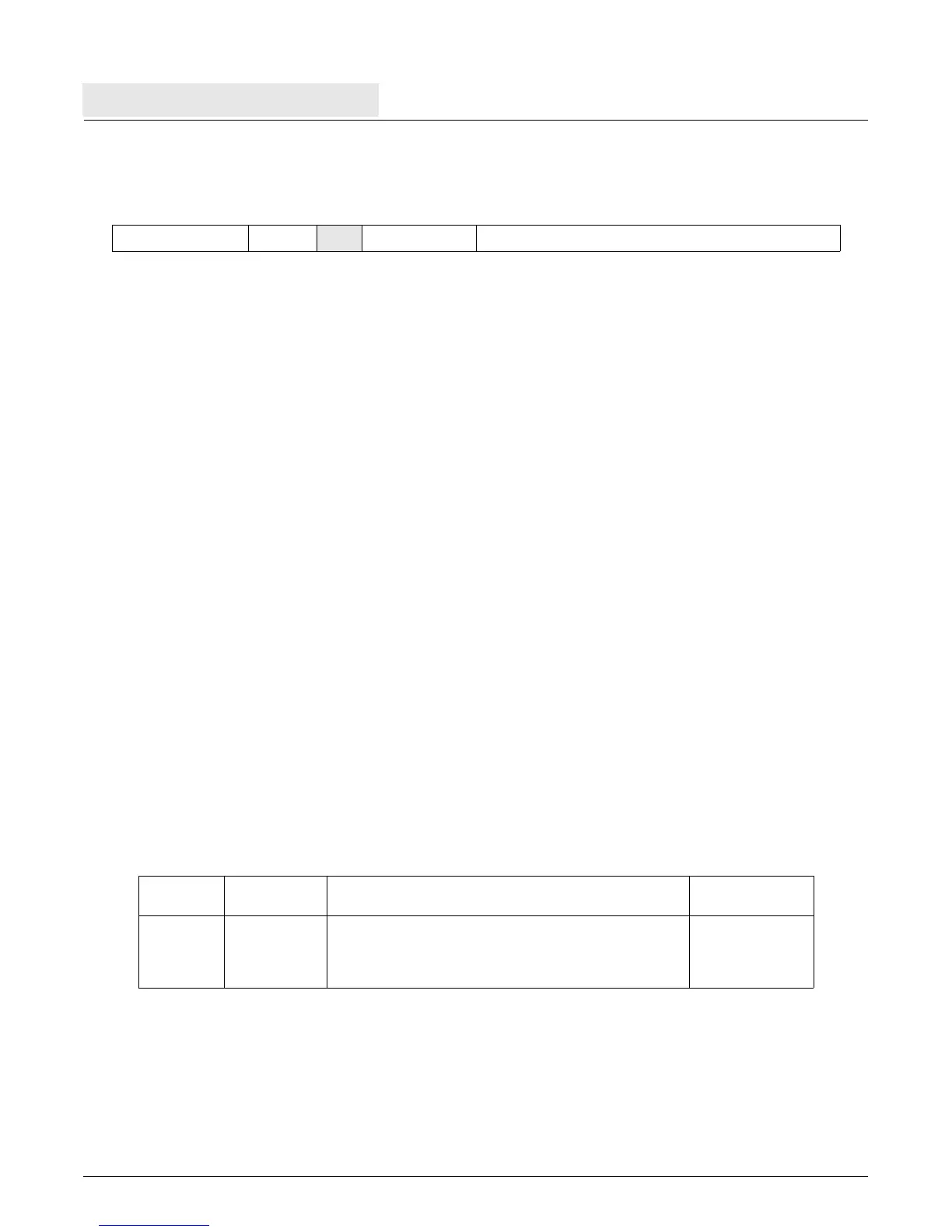

cmpli BF, 0, RA, IM

10 BF

RA IM

0691116 31

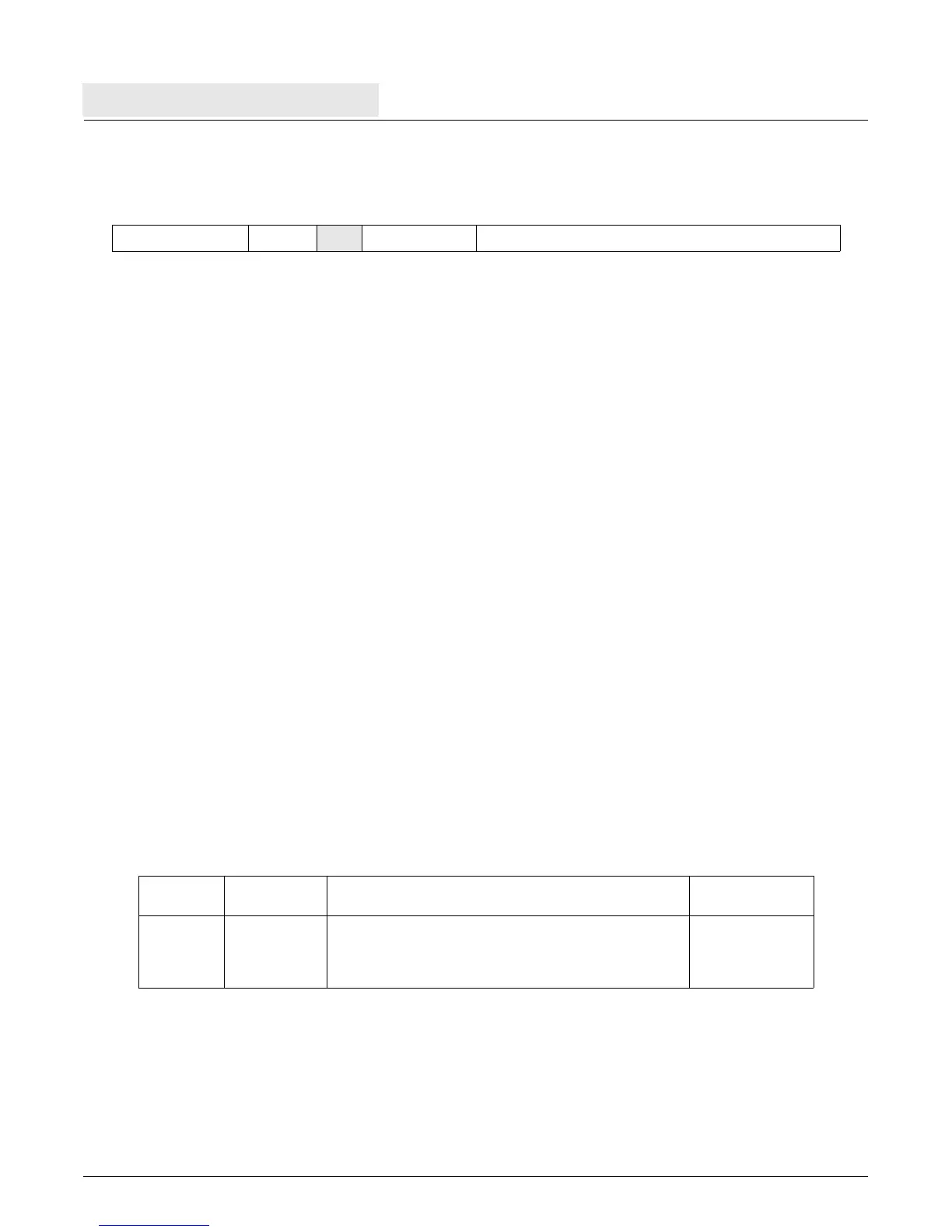

Table 9-13. Extended Mnemonics for cmpli

Mnemonic Operands Function

Other Registers

Changed

cmplwi [BF,] RA, IM

Compare Logical Word Immediate.

Use CR0 if BF is omitted.

Extended mnemonic for

cmpli BF,0,RA,IM

<

u

>

u

=

Loading...

Loading...