362 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

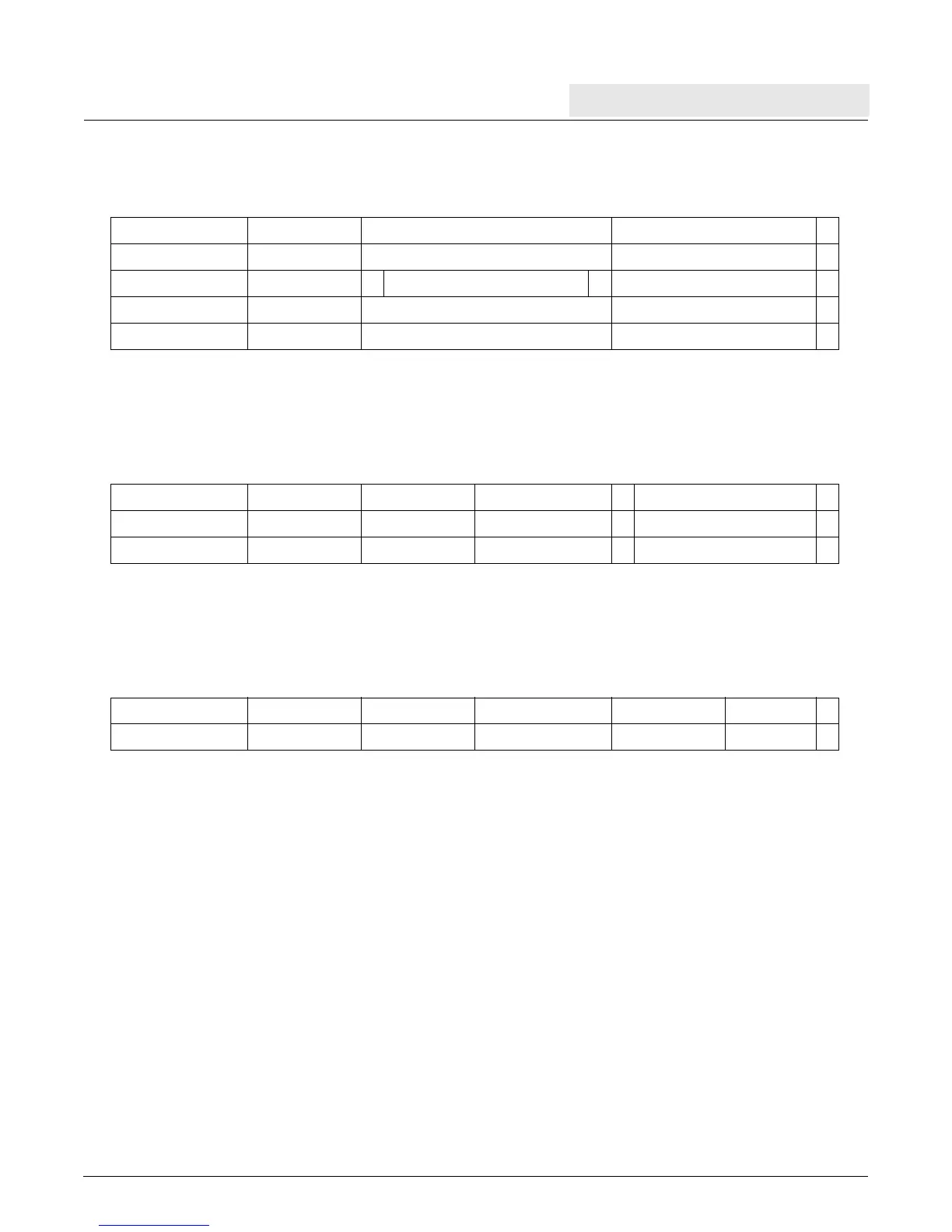

A.1.2.7 XFX-Form

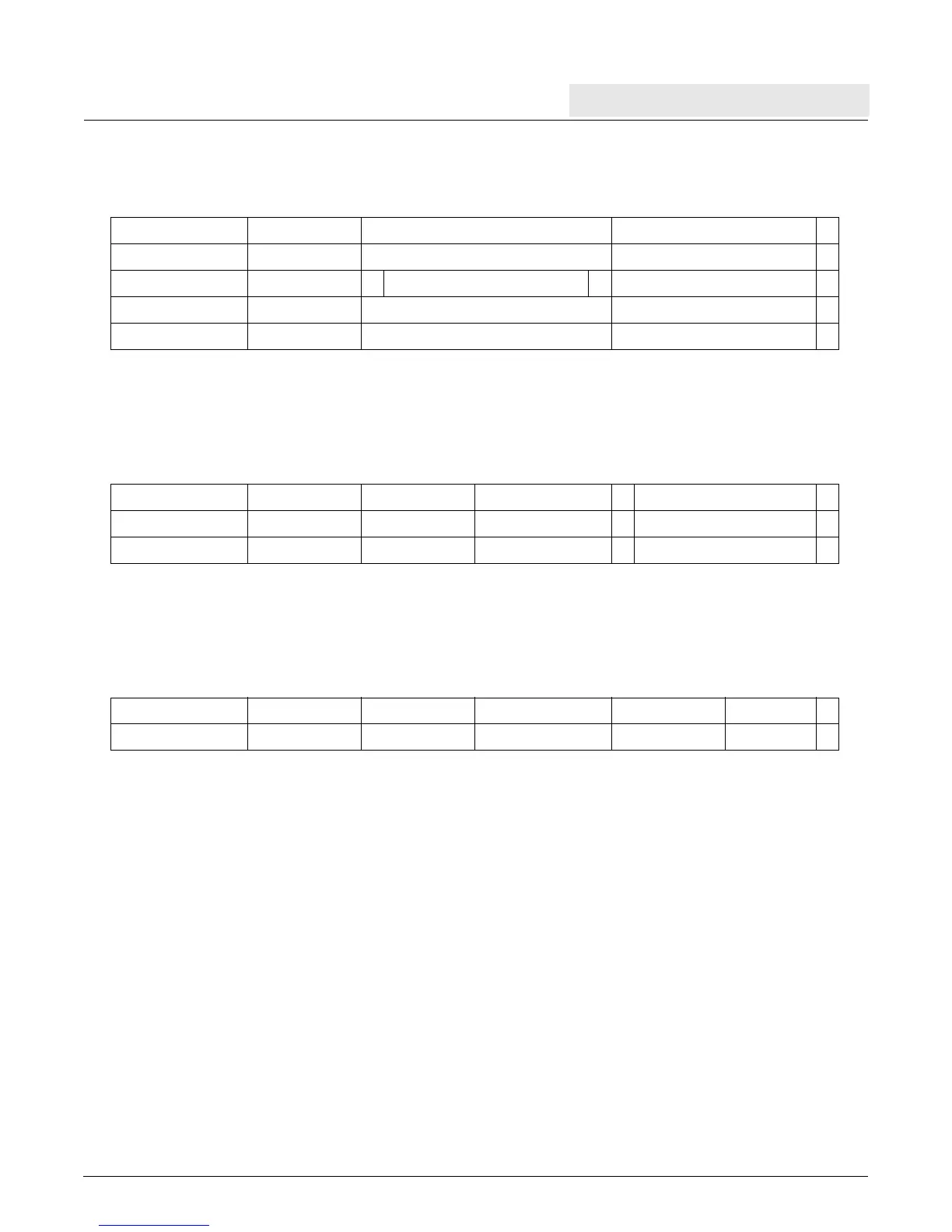

A.1.2.8 X0-Form

A.1.2.9 M-Form

A.2 List of Implemented Instructions—Alphabetical

Table A-1 summarizes the PPC405 instruction set, including required extended mnemonics. All mnemonics are

listed alphabetically, without regard to whether the mnemonic is realized in hardware or software. When an

instruction supports multiple hardware mnemonics (for example, b, ba, bl, bla are all forms of b), the instruction is

alphabetized under the root form. The hardware instructions are described in detail in Instruction Set on page 157

which is also alphabetized under the root form. That section also describes the instruction operands and notation.

Programming Note: Bit 4 of the BO field provides a hint about the most likely outcome of a conditional

branch. (See Branch Prediction on page 52 for a detailed description of branch prediction.) Assemblers should

set BO

4

= 0 unless a specific reason exists otherwise. In the BO field values specified in the table below,

BO

4

= 0 has always been assumed. The assembler must allow the programmer to specify branch prediction.

To do this, the assembler supports a suffixes for the conditional branch mnemonics:

+ Predict branch to be taken.

− Predict branch not to be taken.

Figure A-7. XFX Instruction Format

OPCD RT SPRF XO /

OPCD RT DCRF XO /

OPCD RT / FXM / XO /

OPCD RS SPRF XO /

OPCD RS DCRF XO /

0 6 11 16 21 31

Figure A-8. XO Instruction Format

OPCD RT RA RB OE XO Rc

OPCD RT RA RB OE XO Rc

OPCD RT RA /// / XO Rc

0 6 11 16 21 22 31

Figure A-9. M Instruction Format

OPCD RS RA RB MB

ME

Rc

OPCD RS RA SH MB

ME

Rc

0 6 11 16 21 26 31

Loading...

Loading...