402 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

B.4 Assembler Extended Mnemonics

In the appendix “Assembler Extended Mnemonics” of the PowerPC Architecture, it is required that a PowerPC

assembler support at least a minimal set of extended mnemonics. These mnemonics encode to the opcodes of

other instructions; the only benefit of extended mnemonics is improved usability. Code using extended mnemonics

can be easier to write and to understand. Table B-5 lists the extended mnemonics required for the PPC405.

Note for every Branch Conditional mnemonic:

Bit 4 of the BO field provides a hint about the most likely outcome of a conditional branch. (Branch Prediction on

page 52 describes branch prediction). Assemblers should set BO

4

= 0 unless a specific reason exists otherwise. In

the BO field values specified in the following table, BO

4

= 0 has always been assumed. The assembler must allow

the programmer to specify branch prediction. To do this, the assembler will support a suffix to every conditional

branch mnemonic, as follows:

+ Predict branch to be taken.

– Predict branch not to be taken.

As specific examples, bc also could be coded as bc+ or bc−, and bne also could be coded bne+ or bne−. These

alternate codings set BO

4

= 1 only if the requested prediction differs from the standard prediction (see Branch

Prediction on page 52).

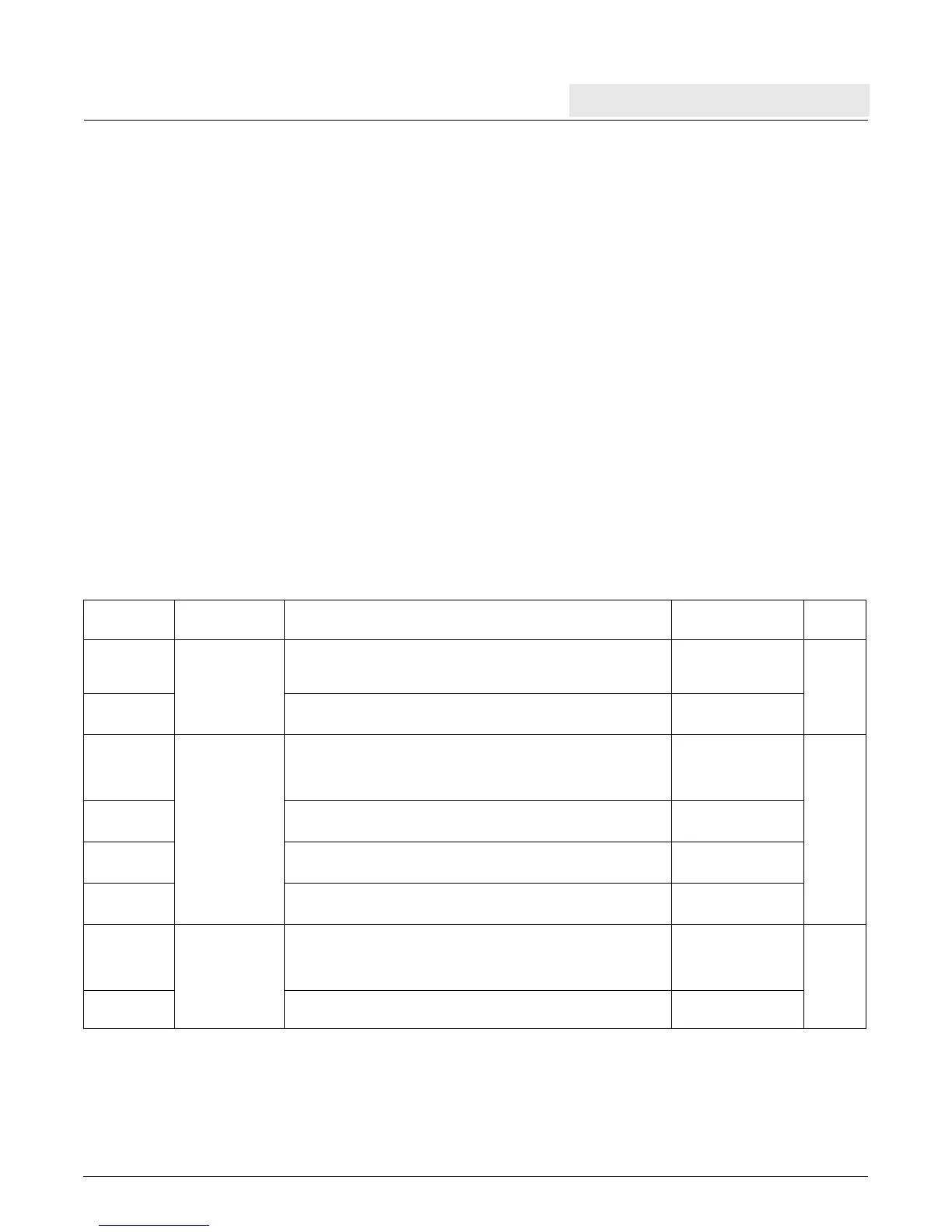

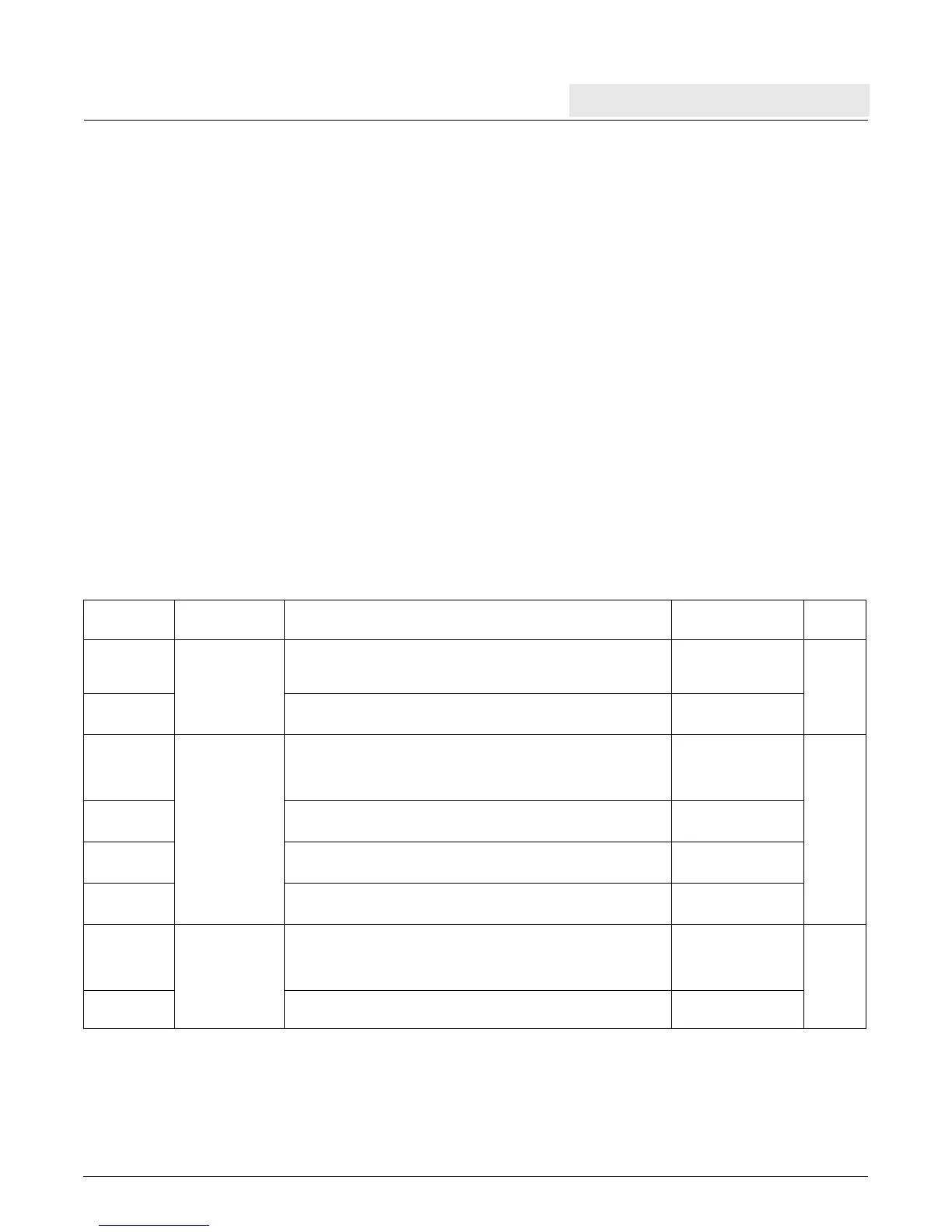

Table B-5. Extended Mnemonics for PPC405

Mnemonic Operands Function

Other Registers

Changed

Page

bctr Branch unconditionally to address in CTR.

Extended mnemonic for

bcctr 20,0

181

bctrl Extended mnemonic for

bcctrl 20,0

(LR) ← CIA + 4

bdnz target Decrement CTR.

Branch if CTR ≠ 0.

Extended mnemonic for

bc 16,0,target

175

bdnza Extended mnemonic for

bca 16,0,target

bdnzl Extended mnemonic for

bcl 16,0,target

(LR) ← CIA + 4.

bdnzla Extended mnemonic for

bcla 16,0,target

(LR) ← CIA + 4.

bdnzlr Decrement CTR.

Branch, if CTR ≠ 0,to address in LR.

Extended mnemonic for

bclr 16,0

175

bdnzlrl Extended mnemonic for

bclrl 16,0

(LR) ← CIA + 4.

Loading...

Loading...