130 AMCC Proprietary

Revision 1.01 - February 19, 2007

PPC405 Processor

Preliminary User’s Manual

7.1 Time Base

The PPC405 implements a 64-bit time base as required in The PowerPC Architecture. The time base, which

increments once during each period of the source clock, provides a time reference.

Read access to the time base is through the mftb instruction. mftb provides user-mode read-only access to the

time base. The TBR numbers (0x10C and 0x10D; TBL and TBU, respectively) that specify the time base registers

to

mftb are not SPR numbers. However, the PowerPC Architecture allows an implementation to handle mftb as

mfspr. Accordingly, these register numbers cannot be used for other SPRs. PowerPC compilers cannot use mftb

with register numbers other than those specified in the PowerPC Architecture as read-access time base registers

(0x10C and 0x10D).

Write access to the time base, using

mtspr, is privileged. Different register numbers are used for read access and

write access. Writing the time base is accomplished by using SPR 0x11C and SPR 0x11D (TBL and TBU, respec-

tively) as operands for

mtspr.

The period of the 64-bit time base is approximately 2925 years for a 200 MHz clock source. The time base does

not generate interrupts, even when it wraps. For most applications, the time base is set once at system reset and

only read thereafter. Note that the FIT and the watchdog timer (discussed below) are driven by 0→1 transitions of

bits from the TBL. Transitions caused by software alteration of TBL have the same effect as transitions caused by

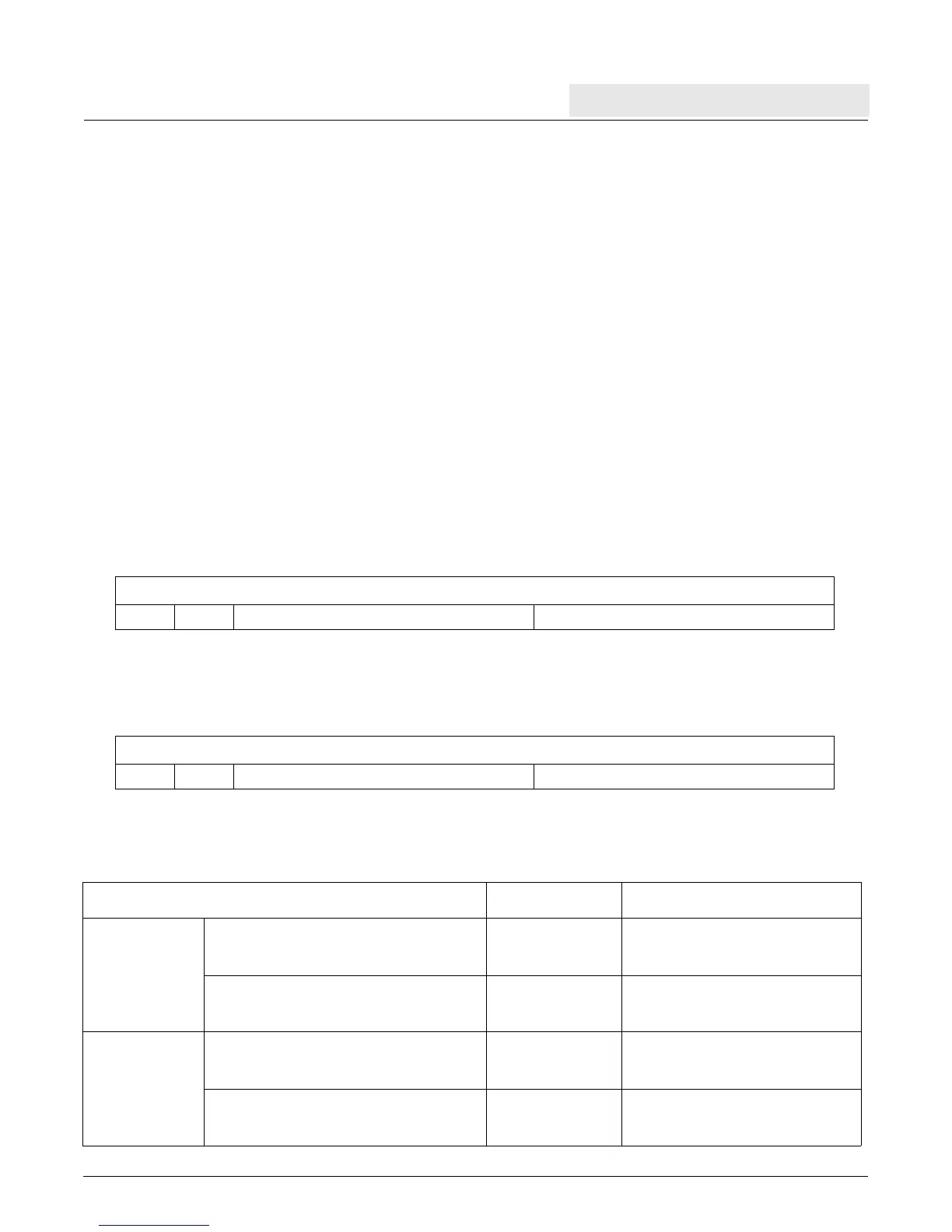

normal incrementing of the time base. Figure 7-2 illustrates the TBL.

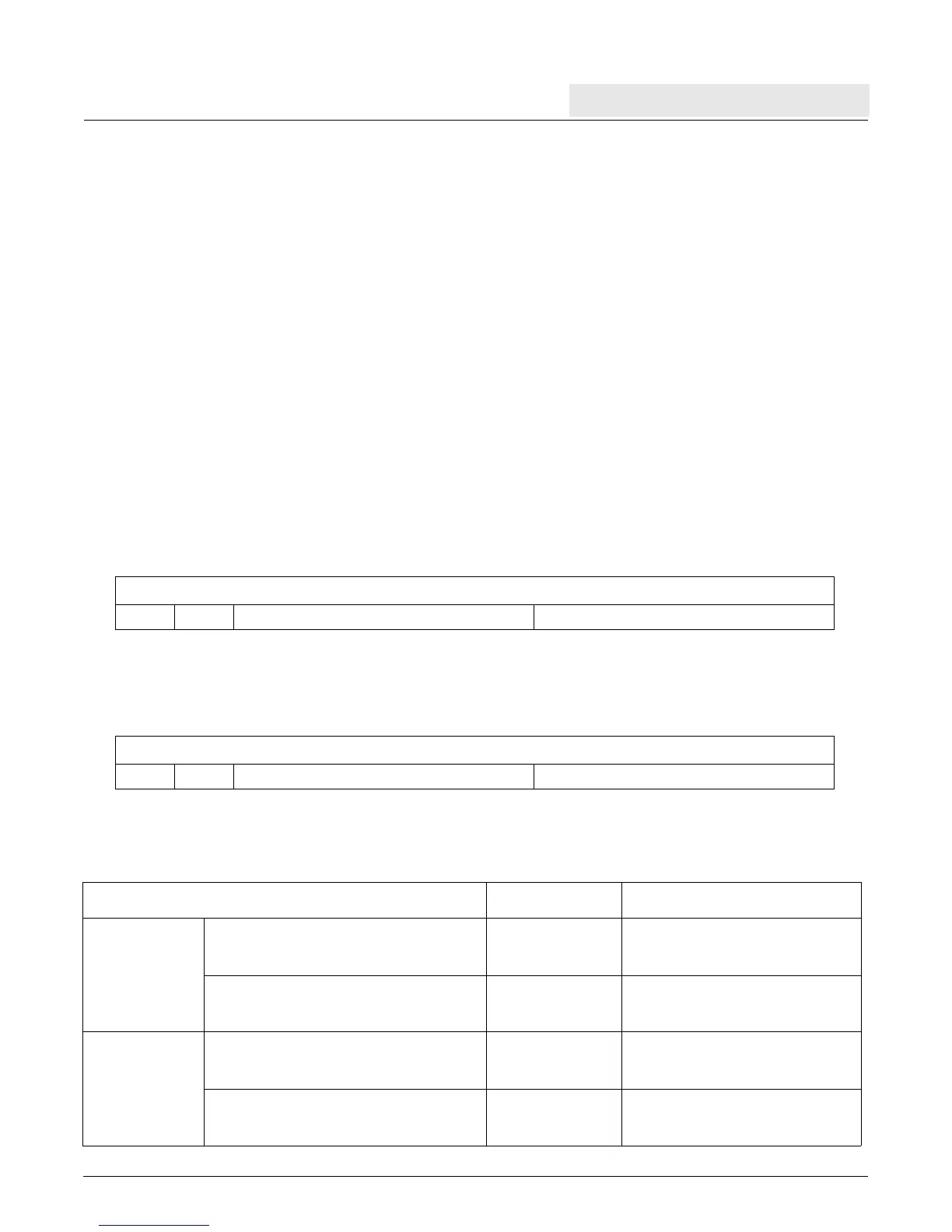

Figure 7-3 illustrates the TBU.

Table 7-1 summarizes the TBRs, instructions used to access the TBRs, and access restrictions.

Figure 7-2. Time Base Lower (TBL)

0:31 Time Base Lower Current count; low-order 32 bits of time base.

Figure 7-3. Time Base Upper (TBU)

0:31 Time Base Upper Current count, high-order 32 bits of time base.

Table 7-1. Time Base Access

Instructions

Register

Number

Access Restrictions

•TBU

• Upper

32 bits

•mftbu RT

• Extended mnemonic for

•mftb RT,TBU

• 0x10D • Read-only

• mttbu RS

• Extended mnemonic for

• mtspr TBU,RS

• 0x11D • Privileged; write-only

•TBL

• Lower

32 bits

•mftb RT

• Extended mnemonic for

•mftb RT,TBL

• 0x10C • Read-only

• mttbl RS

• Extended mnemonic for

• mtspr TBL,RS

• 0x11C • Privileged; write-only

Loading...

Loading...