388 AMCC Proprietary

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

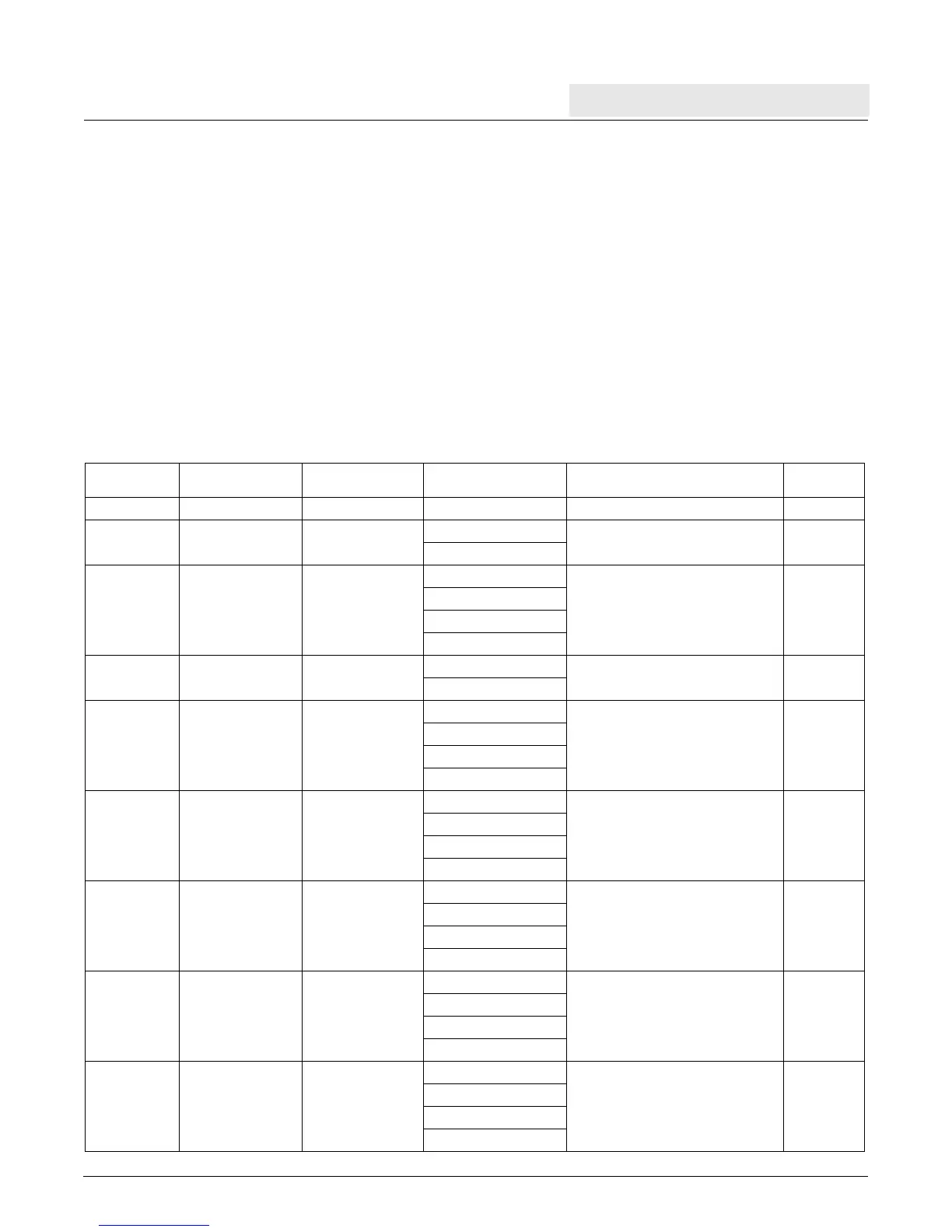

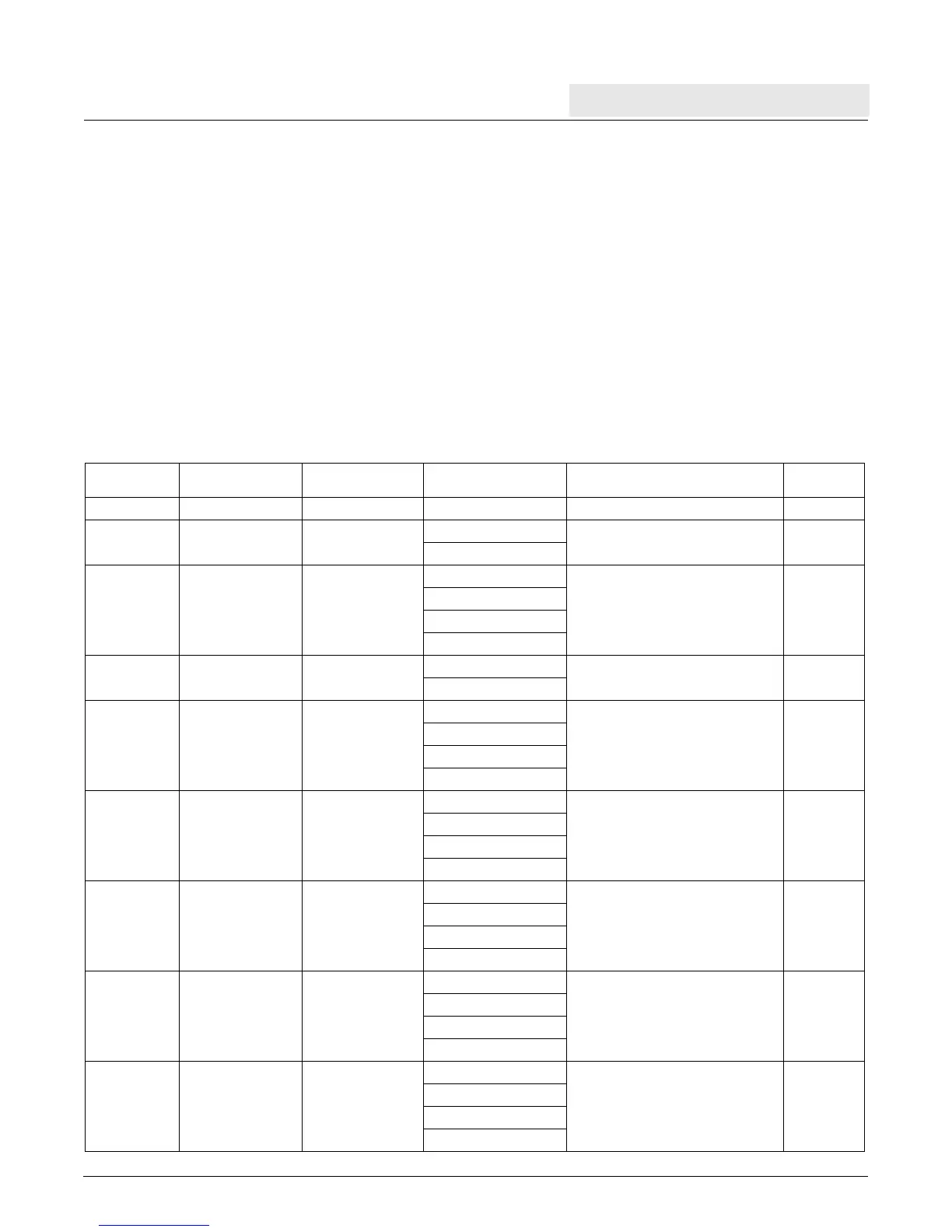

A.3 List of Instructions—by Opcode

All instructions are four bytes long and word aligned. All instructions have a primary opcode field (shown as field

OPCD in Figure A-1 through Figure A-9, beginning on page -360) in bits 0:5. Some instructions also have a

secondary opcode field (shown as field XO in Figure A-1 through Figure A-9). PPC405 instructions, sorted by

primary and secondary opcode, are listed in Table A-2.

The “Form” indicated in the table refers to the arrangement of valid field combinations within the four-byte

instruction. See “Instruction Formats,” on page -357, for the field layouts of each form.

Form X has a 10-bit secondary opcode field, while form XO uses only the low-order 9-bits of that field. Form XO

uses the high-order secondary opcode bit (the tenth bit) as a variable; therefore, every form XO instruction really

consumes two secondary opcodes from the 10-bit secondary-opcode space. The implicitly consumed secondary

opcode is listed in parentheses for form XO instructions in the following table.

Table A-2. PPC405 Instructions by Opcode

Primary

Opcode

Secondary Opcode Form Mnemonic Operands Page

3D

twi

TO, RA, IM 344

48 X

mulhhwu

RT, RA, RB 277

mulhhwu.

4 12 (524) XO

machhwu

RT, RA, RB 256

machhwu.

machhwuo

machhwuo.

440 X

mulhhw

RT, RA, RB 276

mulhhw.

4 44 (556) XO

machhw

RT, RA, RB 253

machhw.

machhwo

machhwo.

4 46 (558) XO

nmachhw

RT, RA, RB 288

nmachhw.

nmachhwo

nmachhwo

4 76 (588) XO

machhwsu

RT, RA, RB 255

machhwsu.

machhwsuo

machhwsuo.

4 108 (620) XO

machhws

RT, RA, RB 254

machhws.

machhwso

machhwso.

4 110 (622) XO

nmachhws

RT, RA, RB 289

nmachhws.

nmachhwso

nmachhwso.

Loading...

Loading...