AMCC Proprietary 155

Revision 1.02 - September 10, 2007

PPC405 Processor

Preliminary User’s Manual

For halfword accesses, the halfword value is replicated in the “empty” halfword in the DVC register, for example, if

the low-order halfword is to be compared, its value is stored in the low-order halfword and the high-order halfword

of the register. Similarly, a byte value is replicated in each byte in the register.

Table 8-7 illustrates comparisons for misaligned DVC accesses. In the “DVC1” and “DVC2” columns, “x” indicates

a don’t care.

Note: Misaligned accesses stop the processor on the instruction causing the compare hit. The second part of an

instruction is not performed if the first part of the compare hits.

8.8.15 Imprecise Debug Event

The imprecise debug event is not an independent debug event, but indicates that a debug event occurred while

MSR[DE] = 0. This is useful in internal debug mode if a debug event occurs while in a critical interrupt handler. On

return from interrupt, a debug interrupt occurs if MSR[DE] = 1. If DBSR[IDE] = 1, the debug event causing the

interrupt occurred sometime earlier, not immediately after a debug event.

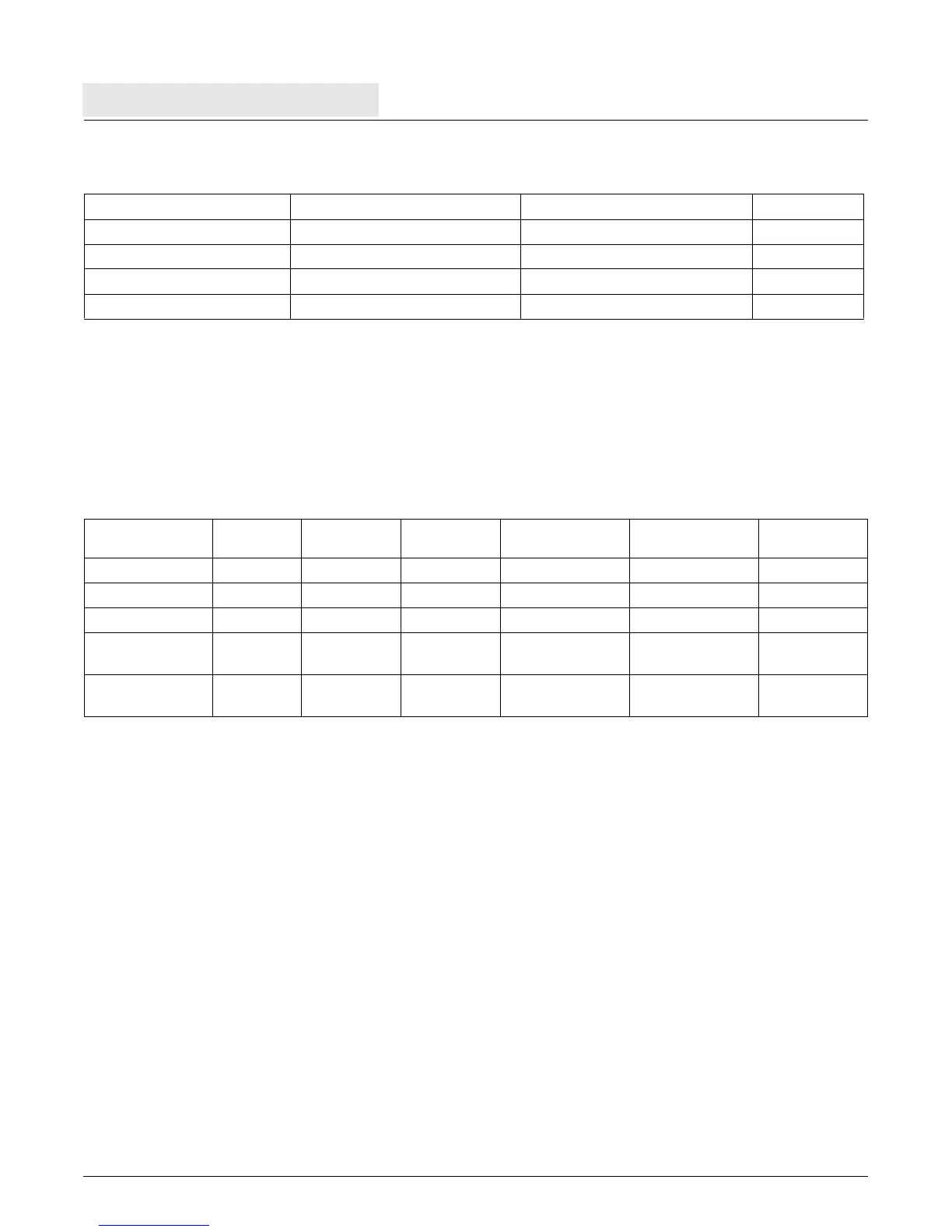

Table 8-6. Comparisons for Aligned DVC Accesses

Access DBCR1[DVnBE] Setting Value Operation

Word All Word value AND

Halfword (Low-Order) All Halfword value replicated AND-OR

Halfword (High-Order) All Halfword value replicated AND-OR

Byte All Byte value replicated OR

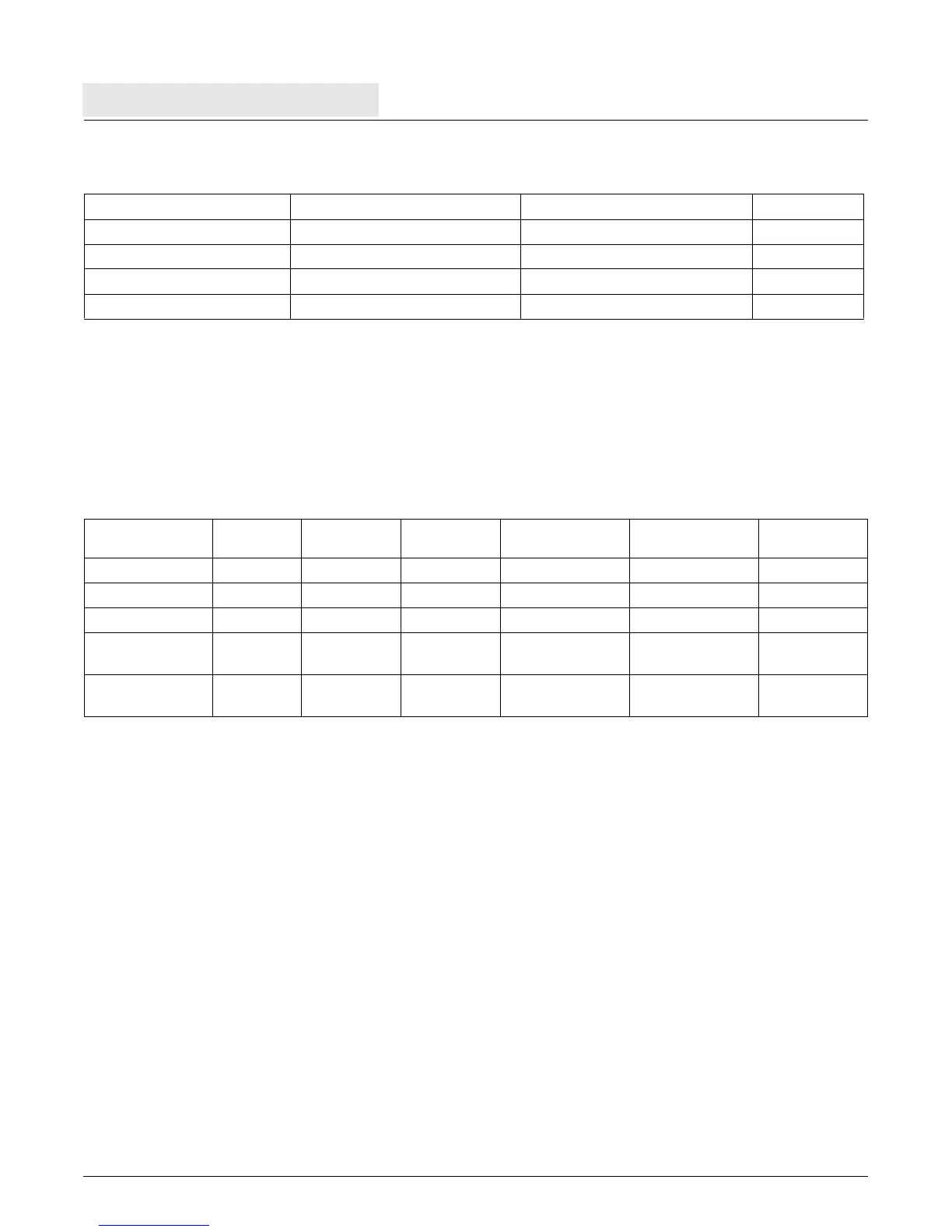

Table 8-7. Comparisons for Misaligned DVC Accesses

Access Operation DVC1 (Hex) DVC2 (Hex)

DBCR1[DV1BE]

Setting

DBCR1[DV2BE]

Setting

DBCR1[D2S]

Setting

Word (Offset 1) AND xx112233 44xxxxxx 123 0 01

Word (Offset 2) AND xxxx1122 3344xxxx 23 01 10

Word (Offset 3) AND xxxxxx11 223344xx 3 012 10

Halfword

(Offset 1)

AND xx1122xx 12 12 10

Halfword

(Offset 3)

AND xxxxxx11 22xxxxxx 3 0 10

Loading...

Loading...